至简设计系列_按键控制数字时钟

–作者:小黑同学

本文为明德扬原创及录用文章,转载请注明出处!

1.1 总体设计

1.1.1 概述

数字时钟是采用数字电路技术实现时、分、秒计时显示的装置,可以用数字同时显示时,分,秒的精确时间并实现准确校时,具备体积小、重量轻、抗干扰能力强、对环境要求高、高精确性、容易开发等特性,在工业控制系统、智能化仪器表、办公自动化系统等诸多领域取得了极为广泛的应用,诸如自动报警、按时自动打铃、时间程序自动控制、定时广播、自定启闭路灯、定时开关烘箱、通断动力设备、甚至各种定时电器的自动启用等。与传统表盘式机械时钟相比,数字时钟具有更高的准确性和直观性,由于没有机械装置,其使用寿命更长。

1.1.2 设计目标

本设计要求实现可设置的数字时钟(速度快10倍,每过0.1s,秒数加1),具体要求如下:

- 按下按键key1,时钟暂停,跳到设置时间状态,在按按键key1,回到正常状态。

- 通过按键key2,选择要设置的位置,初始时设置秒低位,按一下,设置秒高位,再按下,设置分低位,依次类推,循环设置。

- 通过按键key3,设置数值,按一下数值加1,如果溢出,则重新变为0。

- 通过数码管将时间实时显示出来。

- 如果开发板上的按键是矩阵键盘,那么要产生需要的按键信号,需要通过例化矩阵键盘模块来产生。

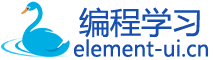

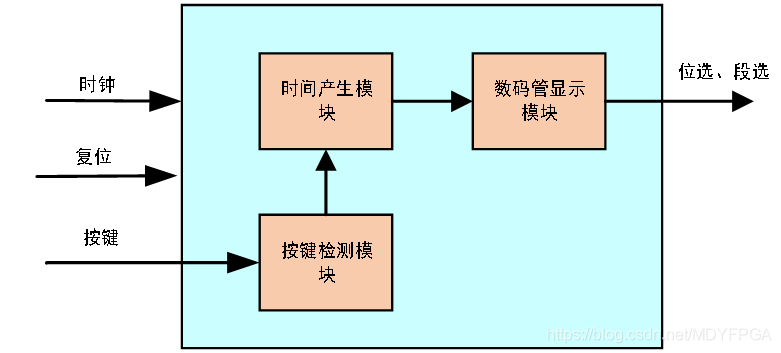

1.1.3 系统结构框图

系统结构框图如下所示:

结构图共分两个,如果使用的开发板上是普通按键的时候,对应的结构图是图一。如果使用的开发板上是矩阵键盘的时候,对应的结构图是图二。

图一

图二

1.1.4 模块功能

按键检测模块实现功能

将外来异步信号打两拍处理,将异步信号同步化;

实现20ms按键消抖功能,并输出有效按键信号。

矩阵键盘模块实现功能

将外来异步信号打两拍处理,将异步信号同步化;

实现20ms按键消抖功能;

实现矩阵键盘的按键检测功能,并输出有效按键信号。

时间产生模块实现功能

产生时间数据;

根据接收到的不同的按键信号,产生暂停、开启、设置时间的功能。

数码管显示模块实现功能

对接收到的时间数据进行译码。

1.1.5 顶层信号

| 信号名 | 接口方向 | 定义 |

|---|---|---|

| clk | 输入 | 系统时钟,50Mhz |

| rst_n | 输入 | 低电平复位信号 |

| Key | 输入 | 3位按键信号,开发板按键为矩阵键盘时,不需要该信号 |

| Key_col | 输入 | 4位矩阵键盘列信号,默认高电平,开发板按键为普通按键时,不需要该信号 |

| Key_row | 输出 | 4位矩阵键盘行信号,默认低电平,开发板按键为普通按键时,不需要该信号 |

| Segment | 输出 | 8位数码管段选信号 |

| Seg_sel | 输出 | 6位数码管位选信号 |

1.1.6 参考代码

下面是使用普通按键的顶层代码:

1.module key_clock(

2. clk ,

3. rst_n ,

4. key ,

5. segment,

6. seg_sel

7.);

8.

9.parameter COUNT_TIME = 23'd500_0000;

10.parameter DELAY_TIME = 10000 ;

11.parameter SEG_WID = 8 ;

12.parameter SEG_SEL = 6 ;

13.

14.parameter KEY_S = 4 ;

15.parameter KEY_W = 3 ;

16.

17.input clk ;

18.input rst_n ;

19.input [ 2:0] key ;

20.output [ 7:0] segment ;

21.output [ 6:0] seg_sel ;

22.

23.wire [ 2:0] key_vld ;

24.wire [23:0] segment_data;

25.wire [ 3:0] cnt2 ;

26.wire [ 3:0] cnt3 ;

27.wire [ 3:0] cnt4 ;

28.wire [ 3:0] cnt5 ;

29.wire [ 3:0] cnt6 ;

30.wire [ 3:0] cnt7 ;

31.

32.

33. key_module uut0(

34. .clk (clk ),

35. .rst_n (rst_n ),

36. .key_in (key ),

37. .key_vld (key_vld)

38. );

39.

40.

41. time_data uut1(

42. .clk (clk ),

43. .rst_n (rst_n ),

44. .key_vld (key_vld),

45. .cnt2 (cnt2 ),

46. .cnt3 (cnt3 ),

47. .cnt4 (cnt4 ),

48. .cnt5 (cnt5 ),

49. .cnt6 (cnt6 ),

50. .cnt7 (cnt7 )

51.

52. );

53.

54.

55. seg_disp uut2(

56. .clk (clk ),

57. .rst_n (rst_n ),

58. .segment (segment ),

59. .seg_sel (seg_sel ),

60. .segment_data (cnt7,cnt6,cnt5,cnt4,cnt3,cnt2)

61.

62. );

63.

64.

65.endmodule

下面是使用矩阵键盘的顶层代码:

66.module key_clock_jvzhen(

67. clk ,

68. rst_n ,

69. key_col,

70. key_row,

71. segment,

72. seg_sel

73.);

74.

75.parameter COUNT_TIME = 23'd500_0000;

76.parameter DELAY_TIME = 10000 ;

77.parameter SEG_WID = 8 ;

78.parameter SEG_SEL = 6 ;

79.

80.parameter KEY_S = 4 ;

81.parameter KEY_W = 3 ;

82.

83.input clk ;

84.input rst_n ;

85.input [ 3:0] key_col ;

86.output [ 3:0] key_row ;

87.output [ 7:0] segment ;

88.output [ 6:0] seg_sel ;

89.

90.wire [ 3:0] key_vld ;

91.wire [ 3:0] cnt2 ;

92.wire [ 3:0] cnt3 ;

93.wire [ 3:0] cnt4 ;

94.wire [ 3:0] cnt5 ;

95.wire [ 3:0] cnt6 ;

96.wire [ 3:0] cnt7 ;

97.

98.

99. key_scan uut0(

100. .clk (clk ),

101. .rst_n (rst_n ),

102. .key_col (key_col),

103. .key_row (key_row),

104. .key_en (key_vld)

105. );

106.

107.

108. time_data uut1(

109. .clk (clk ),

110. .rst_n (rst_n ),

111. .key_vld (key_vld),

112. .cnt2 (cnt2 ),

113. .cnt3 (cnt3 ),

114. .cnt4 (cnt4 ),

115. .cnt5 (cnt5 ),

116. .cnt6 (cnt6 ),

117. .cnt7 (cnt7 )

118.

119. );

120.

121.

122. seg_disp uut2(

123. .clk (clk ),

124. .rst_n (rst_n ),

125. .segment (segment ),

126. .seg_sel (seg_sel ),

127. .segment_data ({cnt7,cnt6,cnt5,cnt4,cnt3,cnt2})

128. );

129.

130.

131.endmodule

1.2 按键检测模块设计

1.2.1 接口信号

| 信号 | 接口方向 | 定义 |

|---|---|---|

| clk | 输入 | 系统时钟 |

| rst_n | 输入 | 低电平复位信号 |

| key_in | 输入 | 按键输入 |

| key_vld | 输出 | 按键按下指示信号 |

1.2.2 设计思路

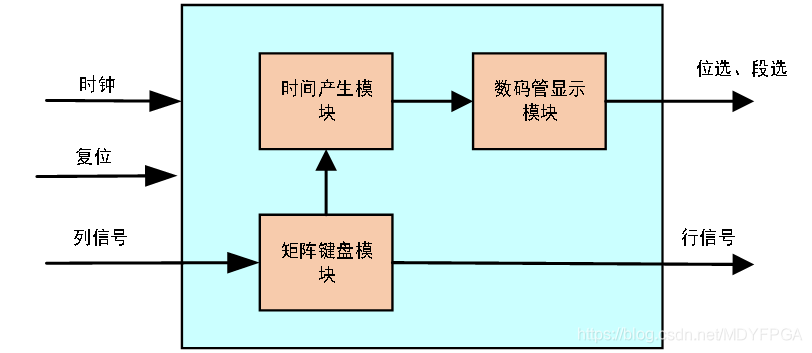

硬件电路

独立式按键工作原理如上图所示,4条输入线连接到FPGA的IO口上,当按键S1按下时,3.3V的电源通过电阻R53再通过按键S1最终进入GND形成一条通路,这条线路的全部电压都加在R53上,则KS0是低电平。当松开按键后,线路断开,就不会有电流通过,KS0应该是3.3V,为高电平。我们可以通过KS0这个IO口的高低电平状态来判断是否有按键按下。其他按键原理与S1一致。

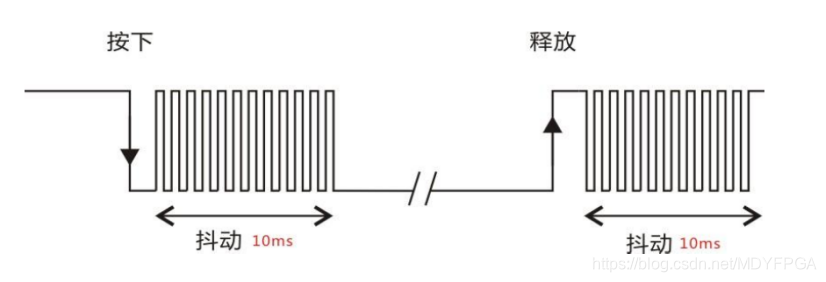

从图上可以看出,如果我们按下按键,那么按键就会接通并连接到低电平GND,如果我们没有按下,那么按键就会断开并接到3.3V,因此按键为低电平有效。通常的按键所用开关为机械弹性开关,当机械触点断开或者闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而机械式按键在闭合及断开的瞬间均伴随有一连串的抖动,如果不进行处理,会使系统识别到抖动信号而进行不必要的反应,导致模块功能不正常,为了避免这种现象的产生,需要进行按键消抖的操作

按键消抖

按键消抖主要分为硬件消抖和软件消抖。两个“与非”门构成一个RS触发器为常用的硬件消抖。软件方法消抖,即检测出键闭合后执行一个延时程序,抖动时间的长短由按键的机械特性决定,一般为5ms~20ms,让前沿抖动消失后再一次检测键的状态,如果仍保持闭合状态电平,则确认按下按键操作有效。当检测到按键释放后,也要给5ms~20ms的延时,待后沿抖动消失后才能转入该键的处理程序。经过按键消抖的行人优先按键,判断按键有效后,按键信号传递给控制系统,控制系统再进入相应的处理程序。

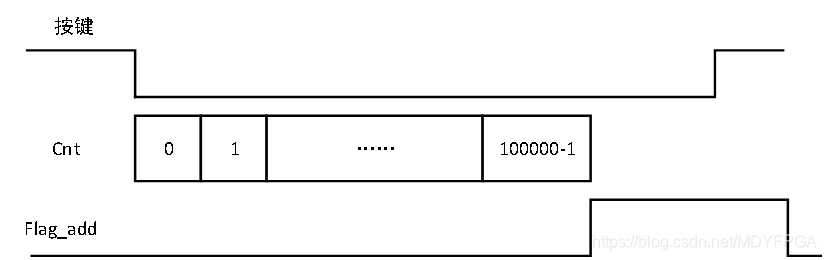

由于按键按下去的时间一般都会大于20ms,为了达到不管按键按下多久,都视为按下一次的效果,提出以下计数器架构,如下图所示:

消抖计数器cnt:用于计算20ms的时间,加一条件为flag==0 &&(&key_in_ff1 == 0),表示当某个按键按下就开始计数;结束条件为100000,表示数到20ms就结束

按键:表示被按下的按键,没被按下时为高电平,按下后为低电平。

Flag_add:20ms指示信号,默认为低电平,当按键按键按下20ms后变为高电平,直到按键信号变为高电平,重新拉低。

1.2.3 参考代码

使用明德扬的计数器模板,可以很快速很熟练地写出按键消抖模块。

132.module key_module(

133. clk ,

134. rst_n ,

135. key_in ,

136. key_vld

137.);

138.parameter DATA_W = 20 ;

139.parameter KEY_W = 3 ;

140.parameter TIME_20MS = 1_000_000 ;

141.

142.input clk ;

143.input rst_n ;

144.input [KEY_W-1 :0] key_in ;

145.output [KEY_W-1 :0] key_vld ;

146.reg [KEY_W-1 :0] key_vld ;

147.reg [DATA_W-1:0] cnt ;

148.wire add_cnt ;

149.wire end_cnt ;

150.reg flag_add ;

151.reg [KEY_W-1 :0] key_in_ff1 ;

152.reg [KEY_W-1 :0] key_in_ff0 ;

153.

154.

155.always @(posedge clk or negedge rst_n)begin

156. if(rst_n==1'b0)begin

157. cnt <= 20'b0;

158. end

159. else if(add_cnt)begin

160. if(end_cnt)

161. cnt <= 20'b0;

162. else

163. cnt <= cnt + 1'b1;

164. end

165. else begin

166. cnt <= 0;

167. end

168.end

169.

170.assign add_cnt = flag_add==1'b0 && (&key_in_ff1==0);

171.assign end_cnt = add_cnt && cnt == TIME_20MS - 1;

172.

173.

174.always @(posedge clk or negedge rst_n)begin

175. if(rst_n==1'b0)begin

176. flag_add <= 1'b0;

177. end

178. else if(end_cnt)begin

179. flag_add <= 1'b1;

180. end

181. else if(&key_in_ff1==1)begin

182. flag_add <= 1'b0;

183. end

184.end

185.

186.

187.always @(posedge clk or negedge rst_n)begin

188. if(rst_n==1'b0)begin

189. key_in_ff0 <= {{KEY_W}{1'b1}};

190. key_in_ff1 <= {{KEY_W}{1'b1}};

191. end

192. else begin

193. key_in_ff0 <= key_in ;

194. key_in_ff1 <= key_in_ff0;

195. end

196.end

197.

198.

199.always @(posedge clk or negedge rst_n)begin

200. if(rst_n==1'b0)begin

201. key_vld <= 0;

202. end

203. else if(end_cnt)begin

204. key_vld <= ~key_in_ff1;

205. end

206. else begin

207. key_vld <= 0;

208. end

209.end

210.

211.

212.endmodule

1.3 矩阵键盘模块设计

1.3.1 接口信号

| 信号 | 接口方向 | 定义 |

|---|---|---|

| clk | 输入 | 系统时钟 |

| rst_n | 输入 | 低电平复位信号 |

| key_col | 输入 | 矩阵键盘列输入信号 |

| Key_row | 输出 | 矩阵键盘行输出信号 |

| Key_en | 输出 | 按键按下指示信号 |

1.3.2 设计思路

在前面的案例中已经有矩阵键盘的介绍,所以这里不在过多介绍,详细介绍请看下方链接:

http://fpgabbs.com/forum.php?mod=viewthread&tid=310

1.3.3 参考代码

1.module key_scan(

2. clk ,

3. rst_n ,

4. key_col,

5. key_row,

6. key_en

7. );

8.

9.

10. parameter KEY_W = 4 ;

11. parameter CHK_COL = 0 ;

12. parameter CHK_ROW = 1 ;

13. parameter DELAY = 2 ;

14. parameter WAIT_END = 3 ;

15. parameter COL_CNT = 16 ;

16. parameter TIME_20MS= 1000000;

17.

18. input clk ;

19. input rst_n ;

20. input [3:0] key_col ;

21.

22. output[3:0] key_en ;

23. output[KEY_W-1:0] key_row ;

24.

25. reg [3:0] key_out ;

26. reg [KEY_W-1:0] key_row ;

27. reg key_vld ;

28.

29.

30. reg [3:0] key_col_ff0 ;

31. reg [3:0] key_col_ff1 ;

32. reg [1:0] key_col_get ;

33. reg [3:0] key_en ;

34. wire end_shake_cnt ;

35. reg end_shake_cnt_ff0;

36. reg [3:0] state_c ;

37. reg [19:0] shake_cnt ;

38. reg [3:0] state_n ;

39. reg [1:0] row_index ;

40. reg [15:0] row_cnt ;

41. wire col2row_start ;

42. wire row2del_start ;

43. wire del2wait_start ;

44. wire wait2col_start ;

45. wire add_row_cnt ;

46. wire end_row_cnt ;

47. wire add_shake_cnt ;

48. wire add_row_index ;

49. wire end_row_index ;

50.

51.

52.always @(posedge clk or negedge rst_n)begin

53. if(rst_n==1'b0)begin

54. key_col_ff0 <= 4'b1111;

55. key_col_ff1 <= 4'b1111;

56. end

57. else begin

58. key_col_ff0 <= key_col ;

59. key_col_ff1 <= key_col_ff0;

60. end

61.end

62.

63.

64.always @(posedge clk or negedge rst_n) begin

65. if (rst_n==0) begin

66. shake_cnt <= 0;

67. end

68. else if(add_shake_cnt) begin

69. if(end_shake_cnt)

70. shake_cnt <= 0;

71. else

72. shake_cnt <= shake_cnt+1 ;

73. end

74.end

75.assign add_shake_cnt = key_col_ff1!=4'hf;

76.assign end_shake_cnt = add_shake_cnt && shake_cnt == TIME_20MS-1 ;

77.

78.

79.always @(posedge clk or negedge rst_n)begin

80. if(rst_n==1'b0)begin

81. state_c <= CHK_COL;

82. end

83. else begin

84. state_c <= state_n;

85. end

86.end

87.

88.always @(*)begin

89. case(state_c)

90. CHK_COL: begin

91. if(col2row_start )begin

92. state_n = CHK_ROW;

93. end

94. else begin

95. state_n = CHK_COL;

96. end

97. end

98. CHK_ROW: begin

99. if(row2del_start)begin

100. state_n = DELAY;

101. end

102. else begin

103. state_n = CHK_ROW;

104. end

105. end

106. DELAY : begin

107. if(del2wait_start)begin

108. state_n = WAIT_END;

109. end

110. else begin

111. state_n = DELAY;

112. end

113. end

114. WAIT_END: begin

115. if(wait2col_start)begin

116. state_n = CHK_COL;

117. end

118. else begin

119. state_n = WAIT_END;

120. end

121. end

122. default: state_n = CHK_COL;

123. endcase

124.end

125.assign col2row_start = state_c==CHK_COL && end_shake_cnt;

126.assign row2del_start = state_c==CHK_ROW && row_index==3 && end_row_cnt;

127.assign del2wait_start= state_c==DELAY && end_row_cnt;

128.assign wait2col_start= state_c==WAIT_END && key_col_ff1==4'hf;

129.

130.always @(posedge clk or negedge rst_n)begin

131. if(rst_n==1'b0)begin

132. key_row <= 4'b0;

133. end

134. else if(state_c==CHK_ROW)begin

135. key_row <= ~(1'b1 << row_index);

136. end

137. else begin

138. key_row <= 4'b0;

139. end

140.end

141.

142.

143.

144.

145.

146.always @(posedge clk or negedge rst_n) begin

147. if (rst_n==0) begin

148. row_index <= 0;

149. end

150. else if(add_row_index) begin

151. if(end_row_index)

152. row_index <= 0;

153. else

154. row_index <= row_index+1 ;

155. end

156. else if(state_c!=CHK_ROW)begin

157. row_index <= 0;

158. end

159.end

160.assign add_row_index = state_c==CHK_ROW && end_row_cnt;

161.assign end_row_index = add_row_index && row_index == 4-1 ;

162.

163.

164.always @(posedge clk or negedge rst_n) begin

165. if (rst_n==0) begin

166. row_cnt <= 0;

167. end

168. else if(add_row_cnt) begin

169. if(end_row_cnt)

170. row_cnt <= 0;

171. else

172. row_cnt <= row_cnt+1 ;

173. end

174.end

175.assign add_row_cnt = state_c==CHK_ROW || state_c==DELAY;

176.assign end_row_cnt = add_row_cnt && row_cnt == 16-1 ;

177.

178.

179.

180.always @(posedge clk or negedge rst_n)begin

181. if(rst_n==1'b0)begin

182. key_col_get <= 0;

183. end

184. else if(state_c==CHK_COL && end_shake_cnt ) begin

185. if(key_col_ff1==4'b1110)

186. key_col_get <= 0;

187. else if(key_col_ff1==4'b1101)

188. key_col_get <= 1;

189. else if(key_col_ff1==4'b1011)

190. key_col_get <= 2;

191. else

192. key_col_get <= 3;

193. end

194.end

195.

196.

197.always @(posedge clk or negedge rst_n)begin

198. if(rst_n==1'b0)begin

199. key_out <= 0;

200. end

201. else if(state_c==CHK_ROW && end_row_cnt)begin

202. key_out <= {row_index,key_col_get};

203. end

204. else begin

205. key_out <= 0;

206. end

207.end

208.

209.always @(posedge clk or negedge rst_n)begin

210. if(rst_n==1'b0)begin

211. key_vld <= 1'b0;

212. end

213. else if(state_c==CHK_ROW && end_row_cnt && key_col_ff1[key_col_get]==1'b0)begin

214. key_vld <= 1'b1;

215. end

216. else begin

217. key_vld <= 1'b0;

218. end

219.end

220.

221.

222.always @(*)begin

223. if(rst_n==1'b0)begin

224. key_en = 0;

225. end

226. else if(key_vld && key_out==0)begin

227. key_en = 4'b0001;

228. end

229. else if(key_vld && key_out==1)begin

230. key_en = 4'b0010;

231. end

232. else if(key_vld && key_out==2)begin

233. key_en = 4'b0100;

234. end

235. else begin

236. key_en = 0;

237. end

238.end

239.

240.

241.Endmodule

1.4 时间产生模块设计

1.4.1 接口信号

| 信号 | 接口方向 | 定义 |

|---|---|---|

| clk | 输入 | 系统时钟 |

| rst_n | 输入 | 低电平复位信号 |

| key_vld | 输入 | 按键按下指示信号 |

| Cnt2 | 输出 | 秒低位计数器 |

| Cnt3 | 输出 | 秒高位计数器 |

| Cnt4 | 输出 | 分低位计数器 |

| Cnt5 | 输出 | 分高位计数器 |

| Cnt6 | 输出 | 时低位计数器 |

| Cnt7 | 输出 | 时高位计数器 |

1.4.2 设计思路

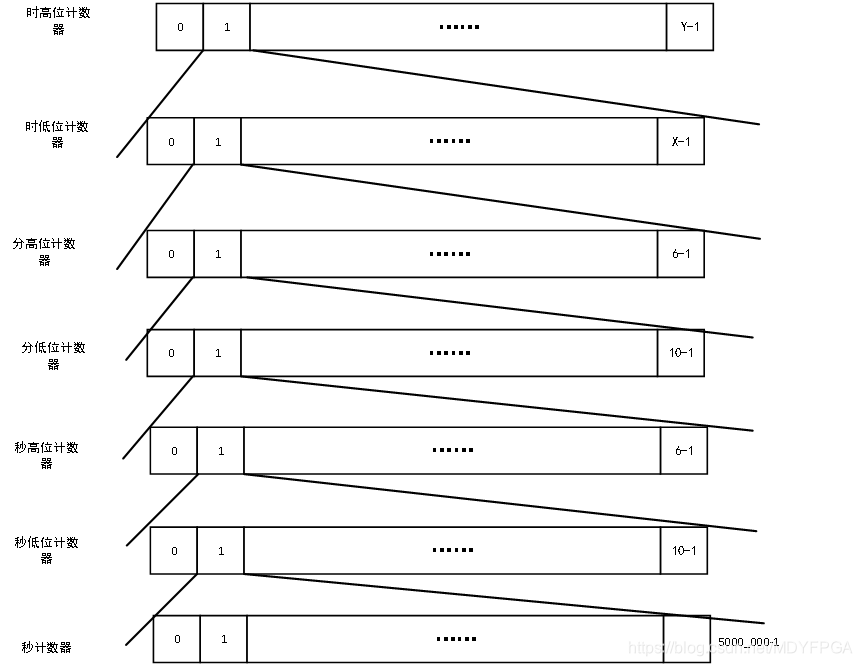

根据题目功能要求可知,要设计数字时钟,由此我们可以提出7个计数器的架构,如下图所示:

该架构由7个计数器组成:时钟计数器cnt1、秒低位计数器cnt2、秒高位计数器cnt3、分低位计数器cnt4、分高位计数器cnt5、时低位计数器cnt6、时高位计数器cnt7。

时钟计数器cnt1:用于计算0.1秒的时钟个数,加一条件为key1_func == 0,表示刚上电时开始计数,key1按下之后停止计数,再按下又重新开始计数;结束条件为5000000,表示数到0.1秒就清零。

秒低位计数器cnt2:用于对“1秒“(实际为0.1秒)进行计数,加一条件为(key1_func &&cnt0 == 0 &&key3_func)||(key1_func == 0 &&end_cnt1),表示在设置状态下可通过按键key3来控制加一,或者在正常状态时数到1秒就加1;结束条件为10,表示数到10秒就清零。

秒高位计数器cnt3:用于对10秒进行计数,加一条件为(key1_func &&cnt0== 1 &&key3_func)||(key1_func== 0 &&end_cnt2),表示在设置状态下可通过按键key3来控制加一,或者在正常状态时数到10秒就加1;结束条件为6,表示数到60秒就清零。

分低位计数器cnt4:用于对1分进行计数,加一条件为(key1_func &&cnt0== 2 &&key3_func)||(key1_func== 0 &&end_cnt3),表示在设置状态下可通过按键key3来控制加一,或者在正常状态时数到1分就加1;结束条件为10,表示数到10分就清零。

分高位计数器cnt5:用于对10分进行计数,加一条件为(key1_func &&cnt0== 3 &&key3_func)||(key1_func== 0 &&end_cnt4),表示在设置状态下可通过按键key3来控制加一,或者在正常状态时数到10分就加1;结束条件为6,表示数到60分就清零。

时低位计数器cnt6:用于对1小时进行计数,加一条件为(key1_func &&cnt0== 4 &&key3_func)||(key1_func== 0 &&end_cnt5),表示在设置状态下可通过按键key3来控制加一,或者在正常状态时数到1小时就加1;结束条件为x,表示数到x小时就清零。

时高位计数器cnt7:用于对10小时进行计数,加一条件为(key1_func &&cnt0== 5 &&key3_func)||(key1_func== 0 &&end_cnt6),表示在设置状态下可通过按键key3来控制加一,或者在正常状态时数到10小时就加1;结束条件为y,表示数到y*10小时就清零。

1.4.3 参考代码

使用明德扬的计数器模板,可以很快速很熟练地写出时间产生模块。

1.module time_data(

2. clk ,

3. rst_n ,

4. key_vld ,

5. cnt2 ,

6. cnt3 ,

7. cnt4 ,

8. cnt5 ,

9. cnt6 ,

10. cnt7

11.);

12.input clk ;

13.input rst_n ;

14.input [ 3:0] key_vld ;

15.output [ 3:0] cnt2 ;

16.output [ 3:0] cnt3 ;

17.output [ 3:0] cnt4 ;

18.output [ 3:0] cnt5 ;

19.output [ 3:0] cnt6 ;

20.output [ 3:0] cnt7 ;

21.

22.reg key1_func ;

23.reg key3_func ;

24.reg [ 2:0] cnt0 ;

25.wire add_cnt0 ;

26.wire end_cnt0 ;

27.reg [ 23:0] cnt1 ;

28.wire add_cnt1 ;

29.wire end_cnt1 ;

30.reg [ 3:0] cnt2 ;

31.wire add_cnt2 ;

32.wire end_cnt2 ;

33.reg [ 3:0] cnt3 ;

34.wire add_cnt3 ;

35.wire end_cnt3 ;

36.reg [ 3:0] cnt4 ;

37.wire add_cnt4 ;

38.wire end_cnt4 ;

39.reg [ 3:0] cnt5 ;

40.wire add_cnt5 ;

41.wire end_cnt5 ;

42.reg [ 3:0] cnt6 ;

43.reg [ 3:0] x ;

44.wire add_cnt6 ;

45.wire end_cnt6 ;

46.reg [ 3:0] cnt7 ;

47.reg [ 1:0] y ;

48.wire add_cnt7 ;

49.wire end_cnt7 ;

50.

51.

52.

53.always @(posedge clk or negedge rst_n)begin

54. if(rst_n==1'b0)begin

55. key1_func<=1'b0;

56. end

57. else if(key_vld[0]==1'b1)begin

58. key1_func<=~key1_func;

59. end

60. else begin

61. key1_func<=key1_func;

62. end

63.end

64.

65.

66.

67.always @(posedge clk or negedge rst_n) begin

68. if (rst_n==0) begin

69. cnt0 <= 0;

70. end

71. else if(add_cnt0) begin

72. if(end_cnt0)

73. cnt0 <= 0;

74. else

75. cnt0 <= cnt0+1 ;

76. end

77.end

78.assign add_cnt0 = key_vld[1];

79.assign end_cnt0 = add_cnt0 && cnt0 == 6-1 ;

80.

81.

82.always @(posedge clk or negedge rst_n)begin

83. if(rst_n==1'b0)begin

84. key3_func<=1'b0;

85. end

86. else if(key1_func==1'b1 && key_vld[2]==1'b1)begin

87. key3_func<=1'b1;

88. end

89. else begin

90. key3_func<=1'b0;

91. end

92.end

93.

94.

95.always @(posedge clk or negedge rst_n) begin

96. if (rst_n==0) begin

97. cnt1 <= 0;

98. end

99. else if(add_cnt1) begin

100. if(end_cnt1)

101. cnt1 <= 0;

102. else

103. cnt1 <= cnt1+1 ;

104. end

105. else begin

106. cnt1 <= 0;

107. end

108.end

109.assign add_cnt1 = key1_func==0;

110.assign end_cnt1 = add_cnt1 && cnt1 == 500_0000-1 ;

111.

112.

113.

114.

115.always @(posedge clk or negedge rst_n) begin

116. if (rst_n==0) begin

117. cnt2 <= 0;

118. end

119. else if(add_cnt2) begin

120. if(end_cnt2)

121. cnt2 <= 0;

122. else

123. cnt2 <= cnt2+1 ;

124. end

125.end

126.assign add_cnt2 = (key1_func && cnt0==0 && key3_func) || (key1_func==0 && end_cnt1);

127.assign end_cnt2 = add_cnt2 && cnt2 == 10-1 ;

128.

129.

130.

131.

132.always @(posedge clk or negedge rst_n) begin

133. if (rst_n==0) begin

134. cnt3 <= 0;

135. end

136. else if(add_cnt3) begin

137. if(end_cnt3)

138. cnt3 <= 0;

139. else

140. cnt3 <= cnt3+1 ;

141. end

142.end

143.assign add_cnt3 = (key1_func && cnt0==1 && key3_func) || (key1_func==0 && end_cnt2);

144.assign end_cnt3 = add_cnt3 && cnt3 == 6-1 ;

145.

146.

147.

148.always @(posedge clk or negedge rst_n) begin

149. if (rst_n==0) begin

150. cnt4 <= 0;

151. end

152. else if(add_cnt4) begin

153. if(end_cnt4)

154. cnt4 <= 0;

155. else

156. cnt4 <= cnt4+1 ;

157. end

158.end

159.assign add_cnt4 = (key1_func && cnt0==2 && key3_func) || (key1_func==0 && end_cnt3);

160.assign end_cnt4 = add_cnt4 && cnt4 == 10-1 ;

161.

162.

163.always @(posedge clk or negedge rst_n) begin

164. if (rst_n==0) begin

165. cnt5 <= 0;

166. end

167. else if(add_cnt5) begin

168. if(end_cnt5)

169. cnt5 <= 0;

170. else

171. cnt5 <= cnt5+1 ;

172. end

173.end

174.assign add_cnt5 = (key1_func && cnt0==3 && key3_func) || (key1_func==0 && end_cnt4);

175.assign end_cnt5 = add_cnt5 && cnt5 == 6-1 ;

176.

177.

178.always @(posedge clk or negedge rst_n) begin

179. if (rst_n==0) begin

180. cnt6 <= 0;

181. end

182. else if(add_cnt6) begin

183. if(end_cnt6)

184. cnt6 <= 0;

185. else

186. cnt6 <= cnt6+1 ;

187. end

188.end

189.assign add_cnt6 = (key1_func && cnt0==4 && key3_func) || (key1_func==0 && end_cnt5);

190.assign end_cnt6 = add_cnt6 && cnt6 == x-1 ;

191.

192.

193.

194.always @(posedge clk or negedge rst_n) begin

195. if (rst_n==0) begin

196. cnt7 <= 0;

197. end

198. else if(add_cnt7) begin

199. if(end_cnt7)

200. cnt7 <= 0;

201. else

202. cnt7 <= cnt7+1 ;

203. end

204.end

205.assign add_cnt7 = (key1_func && cnt0==5 && key3_func) || (key1_func==0 && end_cnt6);

206.assign end_cnt7 = add_cnt7 && cnt7 == y-1 ;

207.

208.

209.always @(*)begin

210. if(cnt7==2)begin

211. x = 4;

212. end

213. else begin

214. x =10;

215. end

216.end

217.

218.always @(*)begin

219. if(cnt6>=4)begin

220. y = 2;

221. end

222. else begin

223. y = 3;

224. end

225.end

226.

227.

228.endmodule

1.5 数码管显示模块设计

1.5.1 接口信号

| 信号 | 接口方向 | 定义 |

|---|---|---|

| clk | 输入 | 系统时钟 |

| rst_n | 输入 | 低电平复位信号 |

| Segment_data | 输入 | 时间数据 |

| Segment | 输出 | 数码管段选信号 |

| Seg_sel | 输出 | 数码管位选信号 |

1.5.2 设计思路

在前面的案例中已经有数码管显示的介绍,所以这里不在过多介绍,详细介绍请看下方链接:

http://fpgabbs.com/forum.php?mod=viewthread&tid=399

1.5.3 参考代码

1.module seg_disp(

2. clk ,

3. rst_n ,

4. segment ,

5. segment_data,

6. seg_sel

7.);

8.parameter ZERO = 8'b1100_0000;

9.parameter ONE = 8'b1111_1001;

10.parameter TWO = 8'b1010_0100;

11.parameter THREE = 8'b1011_0000;

12.parameter FOUR = 8'b1001_1001;

13.parameter FIVE = 8'b1001_0010;

14.parameter SIX = 8'b1000_0010;

15.parameter SEVEN = 8'b1111_1000;

16.parameter EIGHT = 8'b1000_0000;

17.parameter NINE = 8'b1001_0000;

18.

19.

20.

21.input clk ;

22.input rst_n ;

23.input [23:0] segment_data;

24.output [ 7:0] segment ;

25.output [ 5:0] seg_sel ;

26.

27.

28.reg [ 7:0] segment ;

29.wire [ 7:0] segment_tmp ;

30.reg [ 5:0] seg_sel ;

31.

32.

33.reg [15:0] cnt8 ;

34.wire add_cnt8 ;

35.wire end_cnt8 ;

36.reg [ 2:0] cnt9 ;

37.wire add_cnt9 ;

38.wire end_cnt9 ;

39.

40.

41.

42.

43.always @(posedge clk or negedge rst_n) begin

44. if (rst_n==0) begin

45. cnt8 <= 0;

46. end

47. else if(add_cnt8) begin

48. if(end_cnt8)

49. cnt8 <= 0;

50. else

51. cnt8 <= cnt8+1 ;

52. end

53.end

54.assign add_cnt8 = 1;

55.assign end_cnt8 = add_cnt8 && cnt8 == 10000-1 ;

56.

57.

58.

59.

60.always @(posedge clk or negedge rst_n) begin

61. if (rst_n==0) begin

62. cnt9 <= 0;

63. end

64. else if(add_cnt9) begin

65. if(end_cnt9)

66. cnt9 <= 0;

67. else

68. cnt9 <= cnt9+1 ;

69. end

70.end

71.assign add_cnt9 = end_cnt8;

72.assign end_cnt9 = add_cnt9 && cnt9 == 6-1 ;

73.

74.

75.

76.

77.assign segment_tmp = segment_data[(1+cnt9)*4-1 -:4];

78.

79.always@(posedge clk or negedge rst_n)begin

80. if(rst_n==1'b0)begin

81. segment<=ZERO;

82. end

83. else begin

84. case(segment_tmp)

85. 4'd0:segment <= ZERO;

86. 4'd1:segment <= ONE;

87. 4'd2:segment <= TWO;

88. 4'd3:segment <= THREE;

89. 4'd4:segment <= FOUR;

90. 4'd5:segment <= FIVE ;

91. 4'd6:segment <= SIX ;

92. 4'd7:segment <= SEVEN ;

93. 4'd8:segment <= EIGHT ;

94. 4'd9:segment <= NINE ;

95. default:begin

96. segment<=segment;

97. end

98. endcase

99. end

100.end

101.

102.

103.

104.

105.always@(posedge clk or negedge rst_n)begin

106. if(rst_n==1'b0)begin

107. seg_sel <= 6'b11_1110;

108. end

109. else begin

110. seg_sel <= ~(6'b1<<cnt9);

111. end

112.end

113.

114.endmodule

1.6 效果和总结

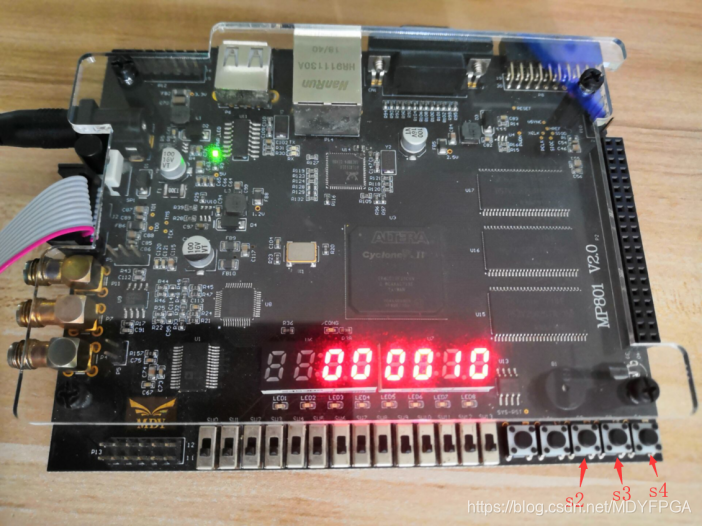

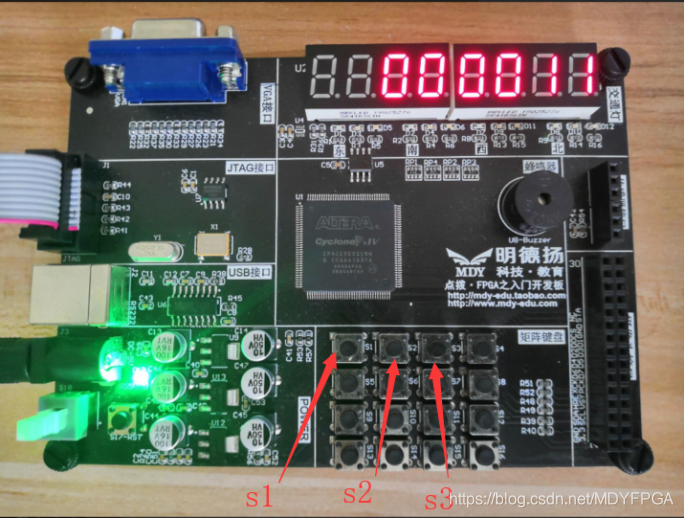

下图是该工程在mp801开发板上的现象

其中按键s4控制数字时钟的暂停与开始,按键s3来选择需要设置的位,按键s2设置数值。

下图是该工程在db603开发板上的现象

其中按键s1控制数字时钟的暂停与开始,按键s2来选择需要设置的位,按键s3设置数值。

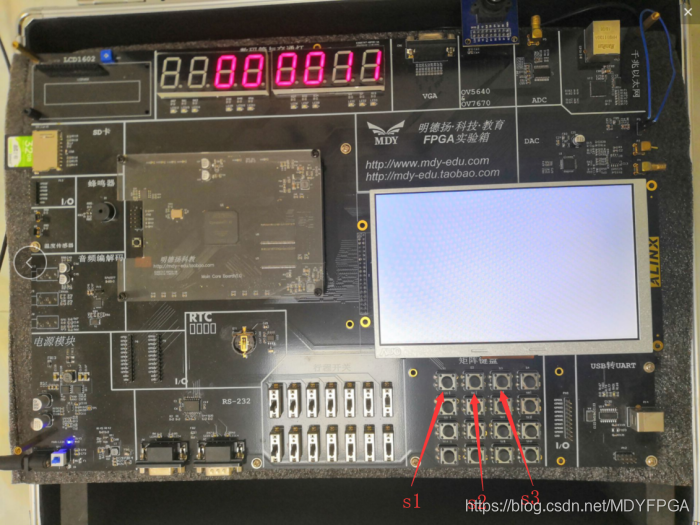

下图是该工程在ms980试验箱上的现象

其中按键s1控制数字时钟的暂停与开始,按键s2来选择需要设置的位,按键s3设置数值。

如若内容造成侵权/违法违规/事实不符,请联系编程学习网邮箱:809451989@qq.com进行投诉反馈,一经查实,立即删除!

相关文章

- 牛客暑假多校 200713F Fake Maxpooling 最小公倍数/单调队列

链接:https://ac.nowcoder.com/acm/contest/5667/F 来源:牛客网 这里题目放在最后了 题意 一个n * m的矩阵 每个元素是行号和列号的最小公倍数 问你矩阵的所有k * k的子矩阵最大值之和为多少。 思路 查了一些方法 说二维st表也行 感觉会mle 但是很多人都说可行 那就可行吧 感…...

2024/4/22 14:52:22 - import pymysql pymysql.install_as_MySQLdb()

import pymysqlpymysql.install_as_MySQLdb()"D:\python364\lib\site-packages\django\db\backends\mysql\base.py注释判断的36行...

2024/4/26 20:42:21 - 机电一体化基础概念以及实训,QY-JDYT05

1、机电一体化的概念: 机电一体化又称机械电子学,它是从系统的观点出发,将机械技术、微电子技术、计算机信息技术、自动控制技术等在系统工程的基础上有机地加以综合,实现整个机械系统最优化而建立起来的一门的科学技术。机电一体化包括机电一体化技术和机电一体化系统两方…...

2024/5/4 15:04:17 - 超星学习通上锁视频进入原理与实现

被老师上锁的视频,我们还能得到平时分吗,这次就教你如何悄悄溜进后台,偷偷改完数据,然后溜出来。 -----如何进入后台进入后台的链接地址: https://mooc1-1.chaoxing.com/moocAnalysis/chapterStatisticByUser?classId=你的classId&courseId=你的courseId&userId=…...

2024/5/4 18:11:46 - 手把手教你怎么样设置QQ透明头像?一个小工具快速搞定!

QQ现在用户量虽没有微信那么多,但是用户量也是非常庞大的,仍然在社交榜排行第二!这么多的用户,虽然昵称和头像都可以自由设置,但大多数都很普通一般! 怎样才能与众不同,有自己的个性呢?今天我们就为大家分享一个独(zhuang)特(B)的技巧,教你设置透明头像,把你的头…...

2024/4/26 3:19:51 - 【Java基础知识】常用的代码托管服务平台

随着互联网的高速发展,进入互联网行业的人越来越多,而且随着开源共享的风气越来越好,因此很多人都会将自己的一些成果上传到网站上与其他人共享,在共享的同时,也可以得到其他人的反馈意见,因此开源可以促进我们一起进步。在互联网上有专门的网站可以帮助我们来管理共享这…...

2024/4/9 19:47:55 - 前端学习笔记1-HTML基础语法

入门基础 一、建立站点(在Dreamweaver环境下) 1、站点作用: 用来归纳一个网站上的所有网页、素材以及他们之间的联系 2、创建站点: (1)创建站点根文件夹(命名规则以字母和下划线开头) (2)根目录下再建文件夹(css:存放所有css文件、image:存放页面内所有图片、js:…...

2024/4/27 6:25:07 - ...mapGetters()

学习vuex过程中 根据文档介绍 https://vuex.vuejs.org/zh-cn/... 和看了 http://www.imooc.com/article/...export default {computed: {...mapGetters([singer]),}....} 最终会转换成export default {computed: {singer() {return this.$store.state.singer}}...}...

2024/4/9 19:47:52 - mybatis的动态SQL之map集合

@Testpublic void testForeachMap(){List<Integer> rids = new ArrayList<Integer>();rids.add(...

2024/4/25 12:04:11 - c# Socket通讯封装类和DEMO

socket封装/// <summary>/// 自定义Socket对象/// </summary>public class Sockets{/// <summary>/// 空构造/// </summary>public Sockets(){}/// <summary>/// 创建Sockets对象/// </summary>/// <param name="ip">Ip地…...

2024/4/26 14:41:50 - 汇编基础(七)之常用跳转指令

指令JMP指令作用作用范围JMP指令转移地址JCXZ指令LOOP循环指令RET指令RETF指令CALL指令语法CALL 标号CALL FAR PTR 标号CALL 寄存器CALL WORD PTR 内存单元地址CALL DWORD PTR 内存单元地址 JMP指令 作用 无条件转移指令,可以只修改IP,也可以同时修改CS和IP。 作用范围 段内短…...

2024/5/2 18:08:57 - 蓝鲸智云部署过程中问题汇总

1:...

2024/5/4 15:03:56 - Redis 有两种持久化方案: RDB和AOF

Redis 有两种持久化方案,RDB (Redis DataBase)和 AOF (Append Only File)1、RDB 是 Redis 默认的持久化方案在指定的时间间隔内,执行指定次数的写操作,则会将内存中的数据写入到磁盘中。即在指定目录下生成一个dump.rdb文件。Redis 重启会通过加载dump.rdb文件恢复数据。…...

2024/4/14 3:59:48 - vue项目使用this.$forceUpdate();强制渲染页面

解决vue this.$forceUpdate() 处理页面刷新问题(v-for循环值刷新等) 问题描述: 在使用Vue框架开发时,在函数中改变了页面中的某个值,在函数中查看是修改成功了,但在页面中没有及时刷新改变后的值: 解决: 运用 this.$forceUpdate()强制刷新 添加this.$forceUpdate();进行强制渲…...

2024/4/15 3:45:50 - SpringBoot整合RocketMQ

SpringBoot整合rocketMQRocketMQRocketmq阿里巴巴开源的一款非常优秀的MQ中间件,现在已经捐赠给Apache成为顶级项目,并且已经成功孵化,而且它是为数不多的支持分布事务消息的中间件。中文文档GitHub 45apache/rocketmq 45Mirror of Apache RocketMQ. Contribute to apache/r…...

2024/4/22 15:09:42 - Java-Stream重用流

** 1. 一个 Stream 只可以使用一次** 多次使用就会报错:stream has already been operated upon or closed,流已经被操作或关闭 ** 2. 解决方法一** 利用Supplier接口重用流 package day12.prepareLesson.c_Stream;import java.sql.SQLOutput; import java.util.function.Sup…...

2024/4/12 8:01:23 - 如何获取微信公众号的关注链接?

一、进入订阅号二、点击右上角按钮三、点击查看历史记录,则进入该公众号的关注页面四、复制该公众号链接,通过该链接就能直接进入关注公众号页面...

2024/5/4 11:58:20 - 计算机网络--Windows网络测试工具

实验目的 理解上述知识点所涉及的基本概念并学会使用这些工具测试网络的状态及从网上获取信息。 实验环境 安装了TCP/IP协议的Windows系统,包含实用的网络工具。 实验内容 完成下列要求,并记录实验步骤和结果 1、 检测本机的MAC地址 2、 检测本机网关的MAC地址 3、 检测本地域…...

2024/4/30 23:43:07 - python读取、写入txt文本内容

参考: 【1】python读取、写入txt文本内容 【2】【python】读取和输出到txt...

2024/4/20 5:18:51 - 前端开发周报——016

1 使用python服务替换nginx服务,使得python既作为静态资源服务又作为动态api服务,这和传统的前后端不分离不一样。2 nginx主要是用作反向代理、负载均衡、静态资源服务的。3 面对复杂的异步流程,相比async,Promise 提供的 all 和 race 会更加好用。4 Symbol 作用是生成…...

2024/5/1 21:23:42

最新文章

- 知识图谱需求

文章目录 公共安全数字经济金融科技资源优化科学研究制造业转型公共健康人文发展 公共安全 公共安全领域信息化以现代通信、网络、数据库技术为基础,将所研究对象各要素汇总至数据库,并针对各个业务领域进行定制化开发,以满足公共安全实战需求…...

2024/5/4 21:08:29 - 梯度消失和梯度爆炸的一些处理方法

在这里是记录一下梯度消失或梯度爆炸的一些处理技巧。全当学习总结了如有错误还请留言,在此感激不尽。 权重和梯度的更新公式如下: w w − η ⋅ ∇ w w w - \eta \cdot \nabla w ww−η⋅∇w 个人通俗的理解梯度消失就是网络模型在反向求导的时候出…...

2024/3/20 10:50:27 - python爬取B站视频

参考:https://cloud.tencent.com/developer/article/1768680 参考的代码有点问题,请求头需要修改,上代码: import requests import re # 正则表达式 import pprint import json from moviepy.editor import AudioFileClip, Vid…...

2024/5/2 17:25:40 - JavaEE 初阶篇-生产者与消费者模型(线程通信)

🔥博客主页: 【小扳_-CSDN博客】 ❤感谢大家点赞👍收藏⭐评论✍ 文章目录 1.0 生产者与消费者模型概述 2.0 在生产者与消费者模型中涉及的关键概念 2.1 缓冲区 2.2 生产者 2.3 消费者 2.4 同步机制 2.5 线程间通信 3.0 实现生产者与消费者模…...

2024/5/2 21:34:51 - 416. 分割等和子集问题(动态规划)

题目 题解 class Solution:def canPartition(self, nums: List[int]) -> bool:# badcaseif not nums:return True# 不能被2整除if sum(nums) % 2 ! 0:return False# 状态定义:dp[i][j]表示当背包容量为j,用前i个物品是否正好可以将背包填满ÿ…...

2024/5/4 12:05:22 - 【Java】ExcelWriter自适应宽度工具类(支持中文)

工具类 import org.apache.poi.ss.usermodel.Cell; import org.apache.poi.ss.usermodel.CellType; import org.apache.poi.ss.usermodel.Row; import org.apache.poi.ss.usermodel.Sheet;/*** Excel工具类** author xiaoming* date 2023/11/17 10:40*/ public class ExcelUti…...

2024/5/4 11:23:32 - Spring cloud负载均衡@LoadBalanced LoadBalancerClient

LoadBalance vs Ribbon 由于Spring cloud2020之后移除了Ribbon,直接使用Spring Cloud LoadBalancer作为客户端负载均衡组件,我们讨论Spring负载均衡以Spring Cloud2020之后版本为主,学习Spring Cloud LoadBalance,暂不讨论Ribbon…...

2024/5/4 14:46:16 - TSINGSEE青犀AI智能分析+视频监控工业园区周界安全防范方案

一、背景需求分析 在工业产业园、化工园或生产制造园区中,周界防范意义重大,对园区的安全起到重要的作用。常规的安防方式是采用人员巡查,人力投入成本大而且效率低。周界一旦被破坏或入侵,会影响园区人员和资产安全,…...

2024/5/3 16:00:51 - VB.net WebBrowser网页元素抓取分析方法

在用WebBrowser编程实现网页操作自动化时,常要分析网页Html,例如网页在加载数据时,常会显示“系统处理中,请稍候..”,我们需要在数据加载完成后才能继续下一步操作,如何抓取这个信息的网页html元素变化&…...

2024/5/4 12:10:13 - 【Objective-C】Objective-C汇总

方法定义 参考:https://www.yiibai.com/objective_c/objective_c_functions.html Objective-C编程语言中方法定义的一般形式如下 - (return_type) method_name:( argumentType1 )argumentName1 joiningArgument2:( argumentType2 )argumentName2 ... joiningArgu…...

2024/5/3 21:22:01 - 【洛谷算法题】P5713-洛谷团队系统【入门2分支结构】

👨💻博客主页:花无缺 欢迎 点赞👍 收藏⭐ 留言📝 加关注✅! 本文由 花无缺 原创 收录于专栏 【洛谷算法题】 文章目录 【洛谷算法题】P5713-洛谷团队系统【入门2分支结构】🌏题目描述🌏输入格…...

2024/5/3 23:17:01 - 【ES6.0】- 扩展运算符(...)

【ES6.0】- 扩展运算符... 文章目录 【ES6.0】- 扩展运算符...一、概述二、拷贝数组对象三、合并操作四、参数传递五、数组去重六、字符串转字符数组七、NodeList转数组八、解构变量九、打印日志十、总结 一、概述 **扩展运算符(...)**允许一个表达式在期望多个参数࿰…...

2024/5/4 14:46:12 - 摩根看好的前智能硬件头部品牌双11交易数据极度异常!——是模式创新还是饮鸩止渴?

文 | 螳螂观察 作者 | 李燃 双11狂欢已落下帷幕,各大品牌纷纷晒出优异的成绩单,摩根士丹利投资的智能硬件头部品牌凯迪仕也不例外。然而有爆料称,在自媒体平台发布霸榜各大榜单喜讯的凯迪仕智能锁,多个平台数据都表现出极度异常…...

2024/5/4 14:46:11 - Go语言常用命令详解(二)

文章目录 前言常用命令go bug示例参数说明 go doc示例参数说明 go env示例 go fix示例 go fmt示例 go generate示例 总结写在最后 前言 接着上一篇继续介绍Go语言的常用命令 常用命令 以下是一些常用的Go命令,这些命令可以帮助您在Go开发中进行编译、测试、运行和…...

2024/5/4 14:46:11 - 用欧拉路径判断图同构推出reverse合法性:1116T4

http://cplusoj.com/d/senior/p/SS231116D 假设我们要把 a a a 变成 b b b,我们在 a i a_i ai 和 a i 1 a_{i1} ai1 之间连边, b b b 同理,则 a a a 能变成 b b b 的充要条件是两图 A , B A,B A,B 同构。 必要性显然࿰…...

2024/5/4 2:14:16 - 【NGINX--1】基础知识

1、在 Debian/Ubuntu 上安装 NGINX 在 Debian 或 Ubuntu 机器上安装 NGINX 开源版。 更新已配置源的软件包信息,并安装一些有助于配置官方 NGINX 软件包仓库的软件包: apt-get update apt install -y curl gnupg2 ca-certificates lsb-release debian-…...

2024/5/3 16:23:03 - Hive默认分割符、存储格式与数据压缩

目录 1、Hive默认分割符2、Hive存储格式3、Hive数据压缩 1、Hive默认分割符 Hive创建表时指定的行受限(ROW FORMAT)配置标准HQL为: ... ROW FORMAT DELIMITED FIELDS TERMINATED BY \u0001 COLLECTION ITEMS TERMINATED BY , MAP KEYS TERMI…...

2024/5/4 12:39:12 - 【论文阅读】MAG:一种用于航天器遥测数据中有效异常检测的新方法

文章目录 摘要1 引言2 问题描述3 拟议框架4 所提出方法的细节A.数据预处理B.变量相关分析C.MAG模型D.异常分数 5 实验A.数据集和性能指标B.实验设置与平台C.结果和比较 6 结论 摘要 异常检测是保证航天器稳定性的关键。在航天器运行过程中,传感器和控制器产生大量周…...

2024/5/4 13:16:06 - --max-old-space-size=8192报错

vue项目运行时,如果经常运行慢,崩溃停止服务,报如下错误 FATAL ERROR: CALL_AND_RETRY_LAST Allocation failed - JavaScript heap out of memory 因为在 Node 中,通过JavaScript使用内存时只能使用部分内存(64位系统&…...

2024/5/4 16:48:41 - 基于深度学习的恶意软件检测

恶意软件是指恶意软件犯罪者用来感染个人计算机或整个组织的网络的软件。 它利用目标系统漏洞,例如可以被劫持的合法软件(例如浏览器或 Web 应用程序插件)中的错误。 恶意软件渗透可能会造成灾难性的后果,包括数据被盗、勒索或网…...

2024/5/4 14:46:05 - JS原型对象prototype

让我简单的为大家介绍一下原型对象prototype吧! 使用原型实现方法共享 1.构造函数通过原型分配的函数是所有对象所 共享的。 2.JavaScript 规定,每一个构造函数都有一个 prototype 属性,指向另一个对象,所以我们也称为原型对象…...

2024/5/4 2:00:16 - C++中只能有一个实例的单例类

C中只能有一个实例的单例类 前面讨论的 President 类很不错,但存在一个缺陷:无法禁止通过实例化多个对象来创建多名总统: President One, Two, Three; 由于复制构造函数是私有的,其中每个对象都是不可复制的,但您的目…...

2024/5/3 22:03:11 - python django 小程序图书借阅源码

开发工具: PyCharm,mysql5.7,微信开发者工具 技术说明: python django html 小程序 功能介绍: 用户端: 登录注册(含授权登录) 首页显示搜索图书,轮播图࿰…...

2024/5/4 9:07:39 - 电子学会C/C++编程等级考试2022年03月(一级)真题解析

C/C++等级考试(1~8级)全部真题・点这里 第1题:双精度浮点数的输入输出 输入一个双精度浮点数,保留8位小数,输出这个浮点数。 时间限制:1000 内存限制:65536输入 只有一行,一个双精度浮点数。输出 一行,保留8位小数的浮点数。样例输入 3.1415926535798932样例输出 3.1…...

2024/5/4 14:46:02 - 配置失败还原请勿关闭计算机,电脑开机屏幕上面显示,配置失败还原更改 请勿关闭计算机 开不了机 这个问题怎么办...

解析如下:1、长按电脑电源键直至关机,然后再按一次电源健重启电脑,按F8健进入安全模式2、安全模式下进入Windows系统桌面后,按住“winR”打开运行窗口,输入“services.msc”打开服务设置3、在服务界面,选中…...

2022/11/19 21:17:18 - 错误使用 reshape要执行 RESHAPE,请勿更改元素数目。

%读入6幅图像(每一幅图像的大小是564*564) f1 imread(WashingtonDC_Band1_564.tif); subplot(3,2,1),imshow(f1); f2 imread(WashingtonDC_Band2_564.tif); subplot(3,2,2),imshow(f2); f3 imread(WashingtonDC_Band3_564.tif); subplot(3,2,3),imsho…...

2022/11/19 21:17:16 - 配置 已完成 请勿关闭计算机,win7系统关机提示“配置Windows Update已完成30%请勿关闭计算机...

win7系统关机提示“配置Windows Update已完成30%请勿关闭计算机”问题的解决方法在win7系统关机时如果有升级系统的或者其他需要会直接进入一个 等待界面,在等待界面中我们需要等待操作结束才能关机,虽然这比较麻烦,但是对系统进行配置和升级…...

2022/11/19 21:17:15 - 台式电脑显示配置100%请勿关闭计算机,“准备配置windows 请勿关闭计算机”的解决方法...

有不少用户在重装Win7系统或更新系统后会遇到“准备配置windows,请勿关闭计算机”的提示,要过很久才能进入系统,有的用户甚至几个小时也无法进入,下面就教大家这个问题的解决方法。第一种方法:我们首先在左下角的“开始…...

2022/11/19 21:17:14 - win7 正在配置 请勿关闭计算机,怎么办Win7开机显示正在配置Windows Update请勿关机...

置信有很多用户都跟小编一样遇到过这样的问题,电脑时发现开机屏幕显现“正在配置Windows Update,请勿关机”(如下图所示),而且还需求等大约5分钟才干进入系统。这是怎样回事呢?一切都是正常操作的,为什么开时机呈现“正…...

2022/11/19 21:17:13 - 准备配置windows 请勿关闭计算机 蓝屏,Win7开机总是出现提示“配置Windows请勿关机”...

Win7系统开机启动时总是出现“配置Windows请勿关机”的提示,没过几秒后电脑自动重启,每次开机都这样无法进入系统,此时碰到这种现象的用户就可以使用以下5种方法解决问题。方法一:开机按下F8,在出现的Windows高级启动选…...

2022/11/19 21:17:12 - 准备windows请勿关闭计算机要多久,windows10系统提示正在准备windows请勿关闭计算机怎么办...

有不少windows10系统用户反映说碰到这样一个情况,就是电脑提示正在准备windows请勿关闭计算机,碰到这样的问题该怎么解决呢,现在小编就给大家分享一下windows10系统提示正在准备windows请勿关闭计算机的具体第一种方法:1、2、依次…...

2022/11/19 21:17:11 - 配置 已完成 请勿关闭计算机,win7系统关机提示“配置Windows Update已完成30%请勿关闭计算机”的解决方法...

今天和大家分享一下win7系统重装了Win7旗舰版系统后,每次关机的时候桌面上都会显示一个“配置Windows Update的界面,提示请勿关闭计算机”,每次停留好几分钟才能正常关机,导致什么情况引起的呢?出现配置Windows Update…...

2022/11/19 21:17:10 - 电脑桌面一直是清理请关闭计算机,windows7一直卡在清理 请勿关闭计算机-win7清理请勿关机,win7配置更新35%不动...

只能是等着,别无他法。说是卡着如果你看硬盘灯应该在读写。如果从 Win 10 无法正常回滚,只能是考虑备份数据后重装系统了。解决来方案一:管理员运行cmd:net stop WuAuServcd %windir%ren SoftwareDistribution SDoldnet start WuA…...

2022/11/19 21:17:09 - 计算机配置更新不起,电脑提示“配置Windows Update请勿关闭计算机”怎么办?

原标题:电脑提示“配置Windows Update请勿关闭计算机”怎么办?win7系统中在开机与关闭的时候总是显示“配置windows update请勿关闭计算机”相信有不少朋友都曾遇到过一次两次还能忍但经常遇到就叫人感到心烦了遇到这种问题怎么办呢?一般的方…...

2022/11/19 21:17:08 - 计算机正在配置无法关机,关机提示 windows7 正在配置windows 请勿关闭计算机 ,然后等了一晚上也没有关掉。现在电脑无法正常关机...

关机提示 windows7 正在配置windows 请勿关闭计算机 ,然后等了一晚上也没有关掉。现在电脑无法正常关机以下文字资料是由(历史新知网www.lishixinzhi.com)小编为大家搜集整理后发布的内容,让我们赶快一起来看一下吧!关机提示 windows7 正在配…...

2022/11/19 21:17:05 - 钉钉提示请勿通过开发者调试模式_钉钉请勿通过开发者调试模式是真的吗好不好用...

钉钉请勿通过开发者调试模式是真的吗好不好用 更新时间:2020-04-20 22:24:19 浏览次数:729次 区域: 南阳 > 卧龙 列举网提醒您:为保障您的权益,请不要提前支付任何费用! 虚拟位置外设器!!轨迹模拟&虚拟位置外设神器 专业用于:钉钉,外勤365,红圈通,企业微信和…...

2022/11/19 21:17:05 - 配置失败还原请勿关闭计算机怎么办,win7系统出现“配置windows update失败 还原更改 请勿关闭计算机”,长时间没反应,无法进入系统的解决方案...

前几天班里有位学生电脑(windows 7系统)出问题了,具体表现是开机时一直停留在“配置windows update失败 还原更改 请勿关闭计算机”这个界面,长时间没反应,无法进入系统。这个问题原来帮其他同学也解决过,网上搜了不少资料&#x…...

2022/11/19 21:17:04 - 一个电脑无法关闭计算机你应该怎么办,电脑显示“清理请勿关闭计算机”怎么办?...

本文为你提供了3个有效解决电脑显示“清理请勿关闭计算机”问题的方法,并在最后教给你1种保护系统安全的好方法,一起来看看!电脑出现“清理请勿关闭计算机”在Windows 7(SP1)和Windows Server 2008 R2 SP1中,添加了1个新功能在“磁…...

2022/11/19 21:17:03 - 请勿关闭计算机还原更改要多久,电脑显示:配置windows更新失败,正在还原更改,请勿关闭计算机怎么办...

许多用户在长期不使用电脑的时候,开启电脑发现电脑显示:配置windows更新失败,正在还原更改,请勿关闭计算机。。.这要怎么办呢?下面小编就带着大家一起看看吧!如果能够正常进入系统,建议您暂时移…...

2022/11/19 21:17:02 - 还原更改请勿关闭计算机 要多久,配置windows update失败 还原更改 请勿关闭计算机,电脑开机后一直显示以...

配置windows update失败 还原更改 请勿关闭计算机,电脑开机后一直显示以以下文字资料是由(历史新知网www.lishixinzhi.com)小编为大家搜集整理后发布的内容,让我们赶快一起来看一下吧!配置windows update失败 还原更改 请勿关闭计算机&#x…...

2022/11/19 21:17:01 - 电脑配置中请勿关闭计算机怎么办,准备配置windows请勿关闭计算机一直显示怎么办【图解】...

不知道大家有没有遇到过这样的一个问题,就是我们的win7系统在关机的时候,总是喜欢显示“准备配置windows,请勿关机”这样的一个页面,没有什么大碍,但是如果一直等着的话就要两个小时甚至更久都关不了机,非常…...

2022/11/19 21:17:00 - 正在准备配置请勿关闭计算机,正在准备配置windows请勿关闭计算机时间长了解决教程...

当电脑出现正在准备配置windows请勿关闭计算机时,一般是您正对windows进行升级,但是这个要是长时间没有反应,我们不能再傻等下去了。可能是电脑出了别的问题了,来看看教程的说法。正在准备配置windows请勿关闭计算机时间长了方法一…...

2022/11/19 21:16:59 - 配置失败还原请勿关闭计算机,配置Windows Update失败,还原更改请勿关闭计算机...

我们使用电脑的过程中有时会遇到这种情况,当我们打开电脑之后,发现一直停留在一个界面:“配置Windows Update失败,还原更改请勿关闭计算机”,等了许久还是无法进入系统。如果我们遇到此类问题应该如何解决呢࿰…...

2022/11/19 21:16:58 - 如何在iPhone上关闭“请勿打扰”

Apple’s “Do Not Disturb While Driving” is a potentially lifesaving iPhone feature, but it doesn’t always turn on automatically at the appropriate time. For example, you might be a passenger in a moving car, but your iPhone may think you’re the one dri…...

2022/11/19 21:16:57