HPS SoC和FPGA联合使用例程

本教程演示了如何使用HPS/ARM与FPGA进行通信。我们将为DE10标准开发板介绍如何根据官方的DE10_Standard_GHRD工程开发出自己的My_GRHD工程。之后,我们会在My_GHRD工程上运行我们自己改造过后的HPS_FPGA_LED应用程序。该应用程序会控制连接到DE10标准开发板上FPGA部分的A的10个LED灯闪烁。其中,LEDR0将会通过闪烁模拟板子的心跳,LEDR1-8将会按照一定频率进行左移右移循环闪烁60次,LEDR9将会在LEDR1-8的每一次循环后闪烁一次。例程中HPS通过Lightweight HPS-to-FPGA Bridge控制FPGA部分连接的LED灯。而且,例程中FPGA部分是由HPS通过HPS中FPGA manager进行配置。

背景要求

假定开发人员已经具有以下背景知识:

FPGA RTL级设计

- 基本的Quartus Prime操作技能

- 基本的RTL编程技能

- 基本的Qsys操作技能

- 关于Memory-Mapped 接口的知识

C语言设计

- 基本的SoC(Embedded Design Suite)操作技能

- C语言编程和编译技巧

- 使用配套的image镜像文件为DE10-Standard板创建Linux引导SD卡的技能

- 在DE10-Standard板上从SD卡引导Linux的技能以及拷贝文件进入DE10-Standard板上Linux文件系统的基本Linux命令操作技能

系统要求

在开始本教程之前,请注意演示项目准备需要以下内容:

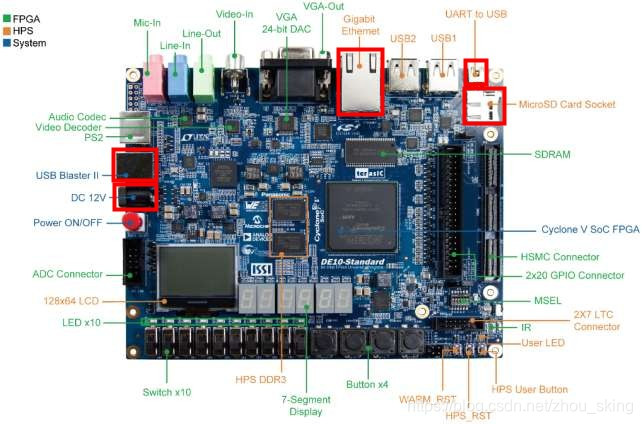

友晶DE10-Standard FPGA板,包括

- 用于串口中断通信的Mini USB线缆

- 存储空间4G以上Micros SD卡

- Micros SD卡读卡器

一台x86架构的PC机

- 装有64位Windows 7操作系统

- 配有一个USB端口

- 装有Quartus Prime 16.1或以上版本

- 装有SoC EDS 16.1 或以上版本

- 装有Win32 Disk Imager软件

Intel SoC FPGA的AXI 桥

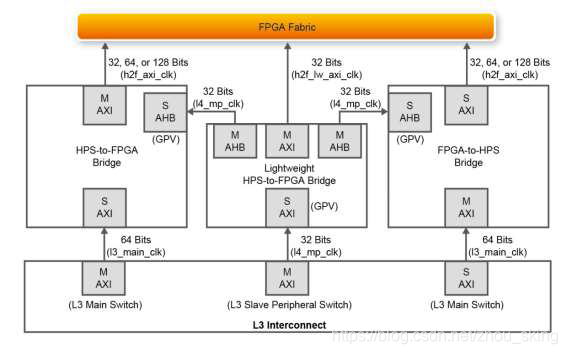

在Intel SoC FPGA中,HPS逻辑与FPGA结构通过AXI(Advanced eXtensible Interface)桥进行连接。为了实现HPS逻辑与FPGA 结构的通信,需要通过使用Intel系统集成工具Qsys添加HPS组件来进行系统设计。从HPS组件的AXI主端口,HPS可以访问那些连接到AXI主端口的内存映射从端口。

HPS包含以下HPS-FPGA AXI桥

- FPGA-to-HPS桥

- HPS-to-FPGA桥

- 轻量级的HPS-to-FPGA桥

下图显示了FPGA结构和L3与HPS互连的AXI桥的框图。每个主(M)接口和从(S)接口显示其数据宽度。括号中标注了每个互连的时钟域。

HPS-to-FPGA桥由3级(L3)主开关控制,轻量级控制HPS-to-FPGA桥由L3从外围从开关控制。

FPGA-to-HPS桥接控制L3主开关,允许任何在FPGA结构的主实现(implemented)去访问在HPS中大多数从实现。

所有三个桥都包含全局程序员视图GPV寄存器。GPV寄存器控制网桥的行为。通过轻量级的HPS-to-FPGA桥访问可以所有三个桥的GPV寄存器。

这个例程向用户介绍了如何使用HPS/ARM与FPGA进行通信。这个与DE10-Standard板上ARM C程序配套的GHRD工程,演示了HPS/ARM程序如何控制连接到FPGA部分的红色LED。

GRHD工程

术语GHRD是黄金硬件参考设计(Golden Hardware Reference Design)的简称。友晶科技为DE10-Standard开发板提供的GRD项目位于CD文件夹中: CD-ROM\Demonstration\SOC_FPGA\ DE10_Standard_GHRD。

本项目由以下组成部分组成:

- ARM Cortex™-A9 MPCore HPS

- 四个用户按钮输入

- 十个用户DIP开关输入

- 10个用户I/O用于LED输出

- 64KB片上存储器

- • JTAG to Avalon master bridges

- Interrupt capturer for use with System Console

- System ID

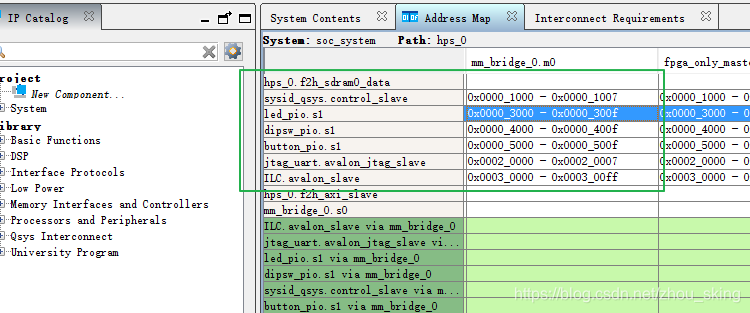

MPU所看到的SoC FPGA部分的系统外围设备的内存映射从轻量级的HPS-to-FPGA到FPGA的基础地址0xFF20_0000开始。MPU可以通过Qsys中的地址偏移来访问这些外围设备。用户可以打开GHRD项目与Quartus II软件。然后打开soc_system。qsys文件与qsys工具。下图列出了连接到轻量级HPS-to-FPGA的外围设备的地址映射。

这些外设的所有Avalon引出信号( Avalon Conduit signals)都连接到DE10-Standard板上SoC FPGA的I/O引脚,如图所示

My_GHRD工程

在实际的应用过程中,友晶科技提供的DE10_Standard_GHRD工程并不是十分契合我们的开发需要,这可能包括外围设备的冗余和不足。下面为了实现本教程开篇所定的目标,我们需要根据DE10_Standard_GHRD工程进行修改。其中友晶科技提供的DE10_Standard_GHRD工程实现的是LEDR0通过闪烁模拟板子的心跳,LEDR1-9按照一定频率进行左移右移循环闪烁60次;我们的目标是LEDR0通过闪烁模拟板子的心跳,LEDR1-8按照一定频率进行左移右移循环闪烁60次,LEDR9在LEDR1-8的每一次循环后闪烁一次。可以看出,我们只需要将DE10_Standard_GHRD工程中的LEDR9的设计进行更改就可以打到我们的目的。下面正式开始更改操作。

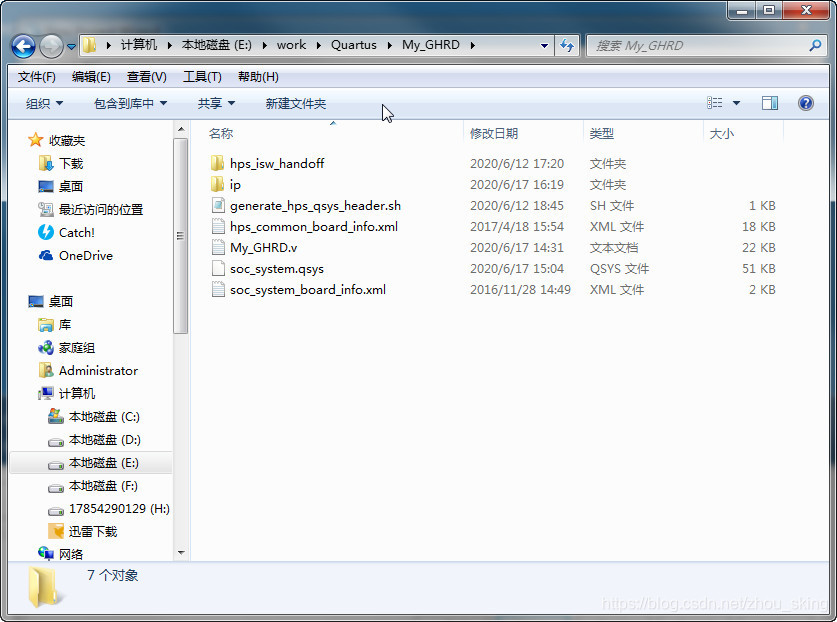

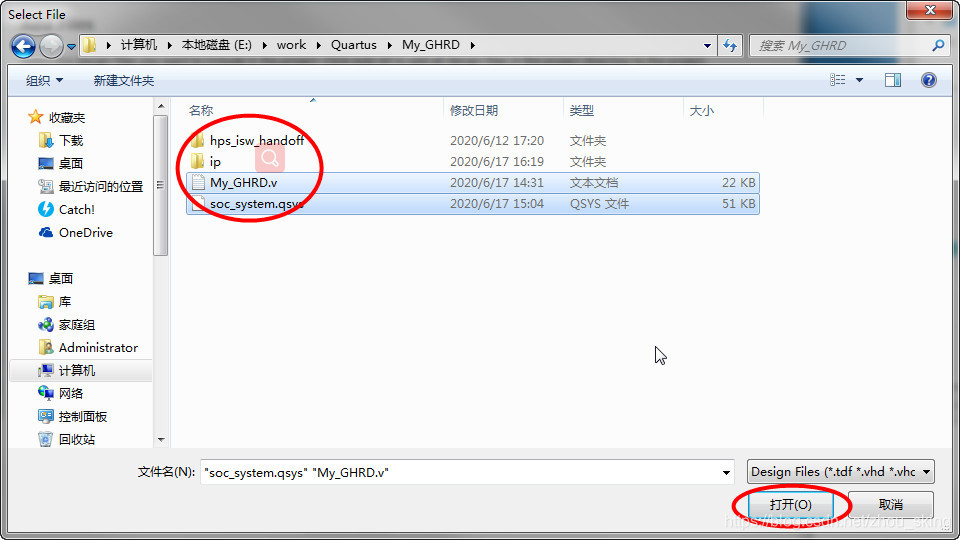

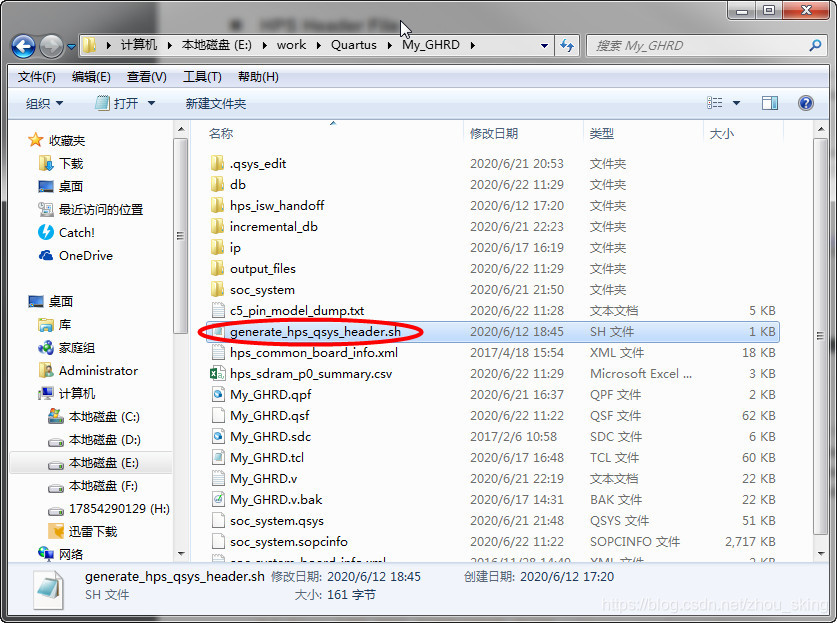

准备设计文件

新建文件夹:E:\work\Quartus\My_GHRD,然后将DE10_Standard_GHRD工程目中的一下文件复制到工程目录下:

- 文件夹:hps_isw_handoff

- 文件夹:ip

- 文件:DE10_Standard_GHRD.v

- 文件:DE10_Standard_GHRD.sdc

- 文件:generate_hps_qsys_header.sh

- 文件:hps_common_board_info.xml

- 文件:soc_system.qsys

- 文件:soc_system_board_info.xml

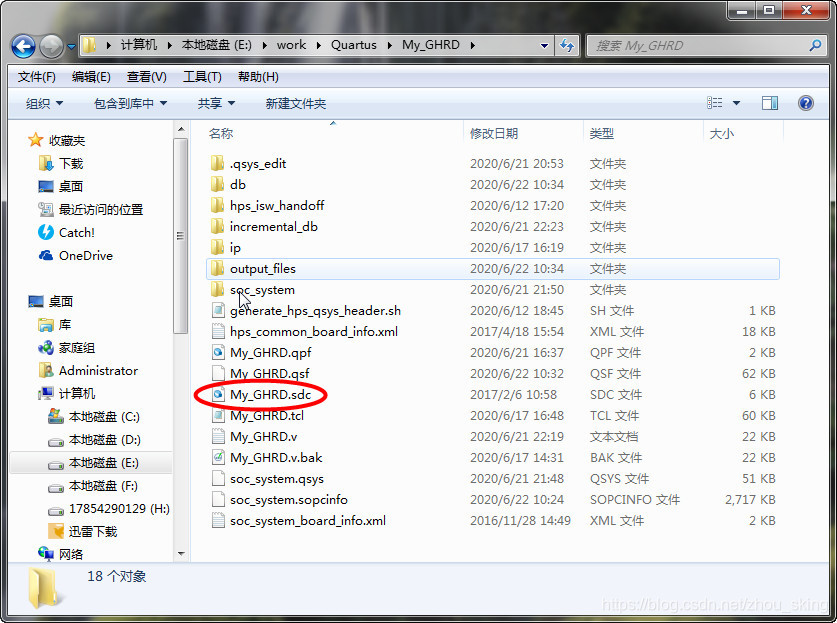

因为其中的文件DE10_Standard_GHRD.v后面将会被指定为顶层文件,所以需要将其更改为与工程名My_GHRD相同的My_GHRD.v文件,同时为了与工程名保持协调,我们也将文件DE10_Standard_GHRD.sdc更改为与工程名My_GHRD相同的My_GHRD.sdc。最终工程目录文件夹如下图所示:

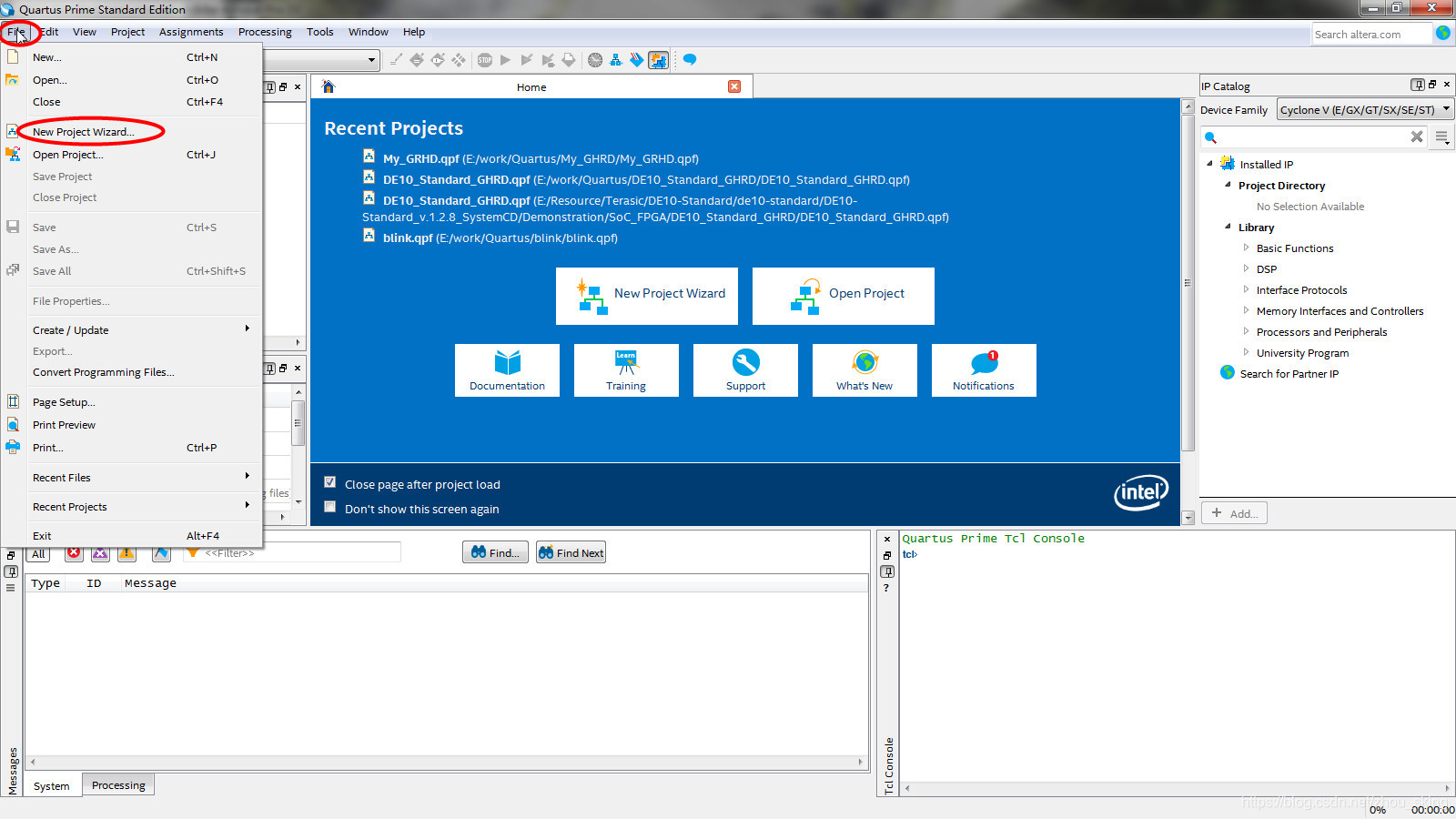

创建My_GHRD工程

首先,建立一个名为:My_GHRD的工程。打开软件Quartus Prime Standard Edition,点击:File→New Project Wizard…,进入工程创建引导界面。

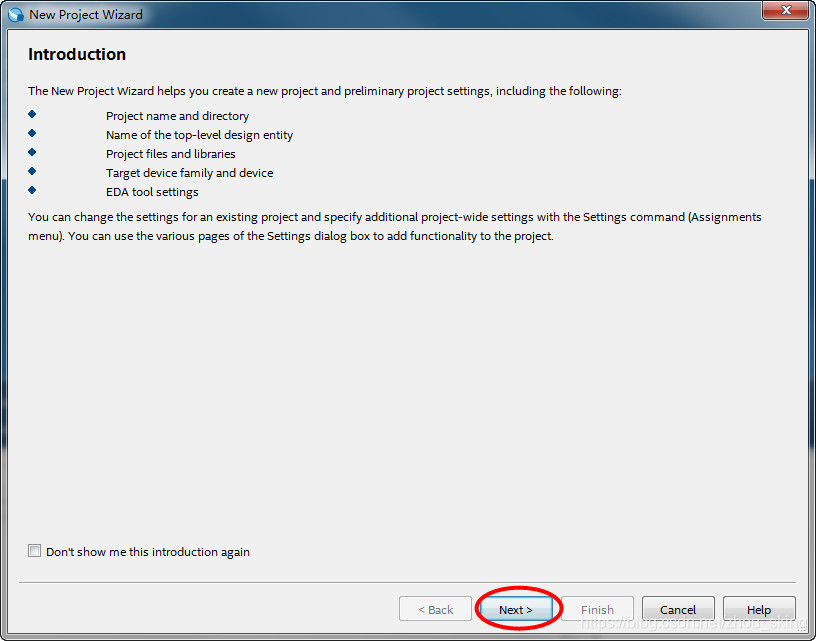

点击引导界面下方的:Next,进入Directory, Name, Top-Level Entity设置界面。

点击右侧按钮:…选择你的工程目录E:/work/Quartus/My_GHRD。之后设置工程名:My_GHRD。此时软件将自动把顶层设计entity name设置为工程名:My_GHRD。继续点击:Next,进入Project Type设置界面。

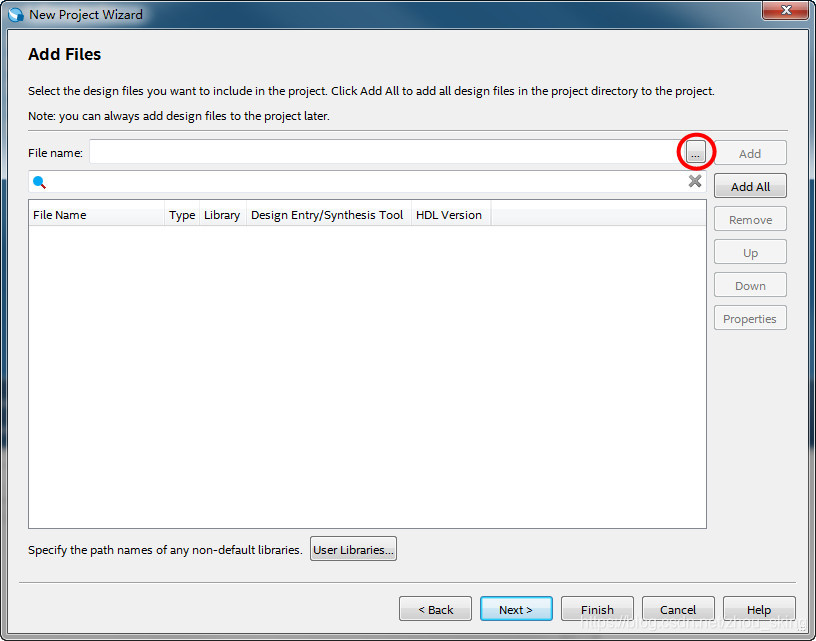

在Project Type界面选择:Empty Project选项,继续点击:Next,进入Add Files设置界面。

在Add Files设置界面,点击右侧按钮:…,添加工程目录下的文件:My_GHRD.v和soc_system.qsys以及文件夹hps_isw_handoff和ip下的所有文件进入工程。

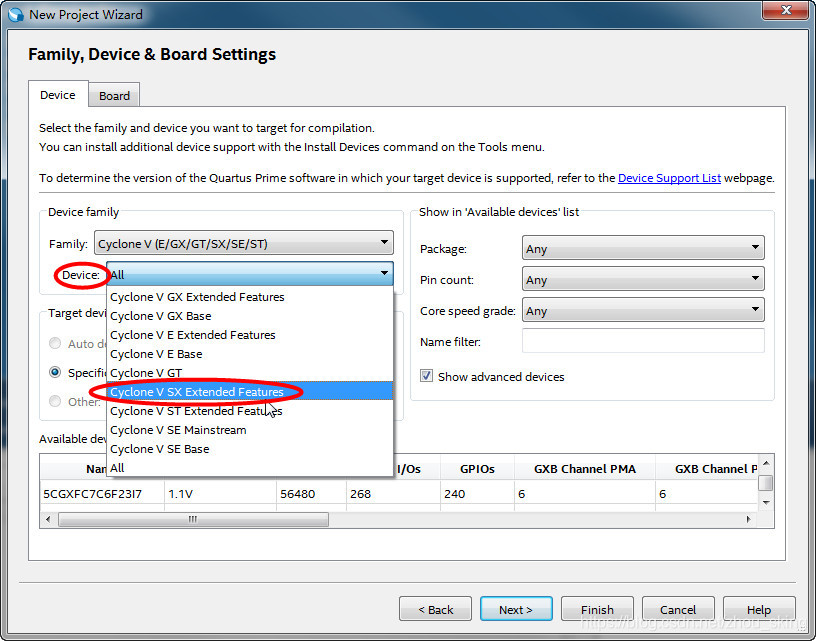

然后点击:Next,进入Family, Device & Board Settings设置界面。

在Family, Device & Board Settings设置界面,我们要设置我们所用的SoC FPGA型号:5CSXFC6D6F31C6N。为了能够快速锁定我们要选择的SoC FPGA型号,我们可以点击:Device下拉列表,选择:Cyclone V SX Extended Features,以缩小选型范围。

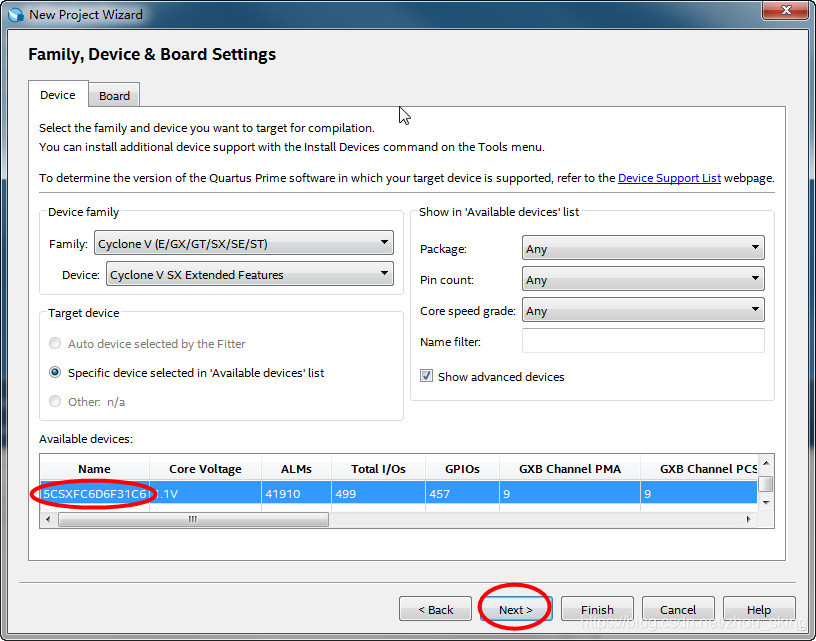

然后,选择Available devices下的5CSXFC6D6F31C6。继续点击:Next,进入EDA Tool Settings设置界面。

在EDA Tool Settings设置界面下,我们保留默认设置。之后点击:Fnish,完成工程创建,退出工程创建引导界面。

Qsys设计

由于我们需要在DE10_Standard_GHRD工程的基础上更改Qsys的设计来实现对LEDR9的单独控制,所以我们需要在Qsys中添加一个1位的PIO端口来实现对LEDR9的控制,同时需要将原来用于同时控制LEDR0-9的10位PIO端口的改为9位的PIO端口。

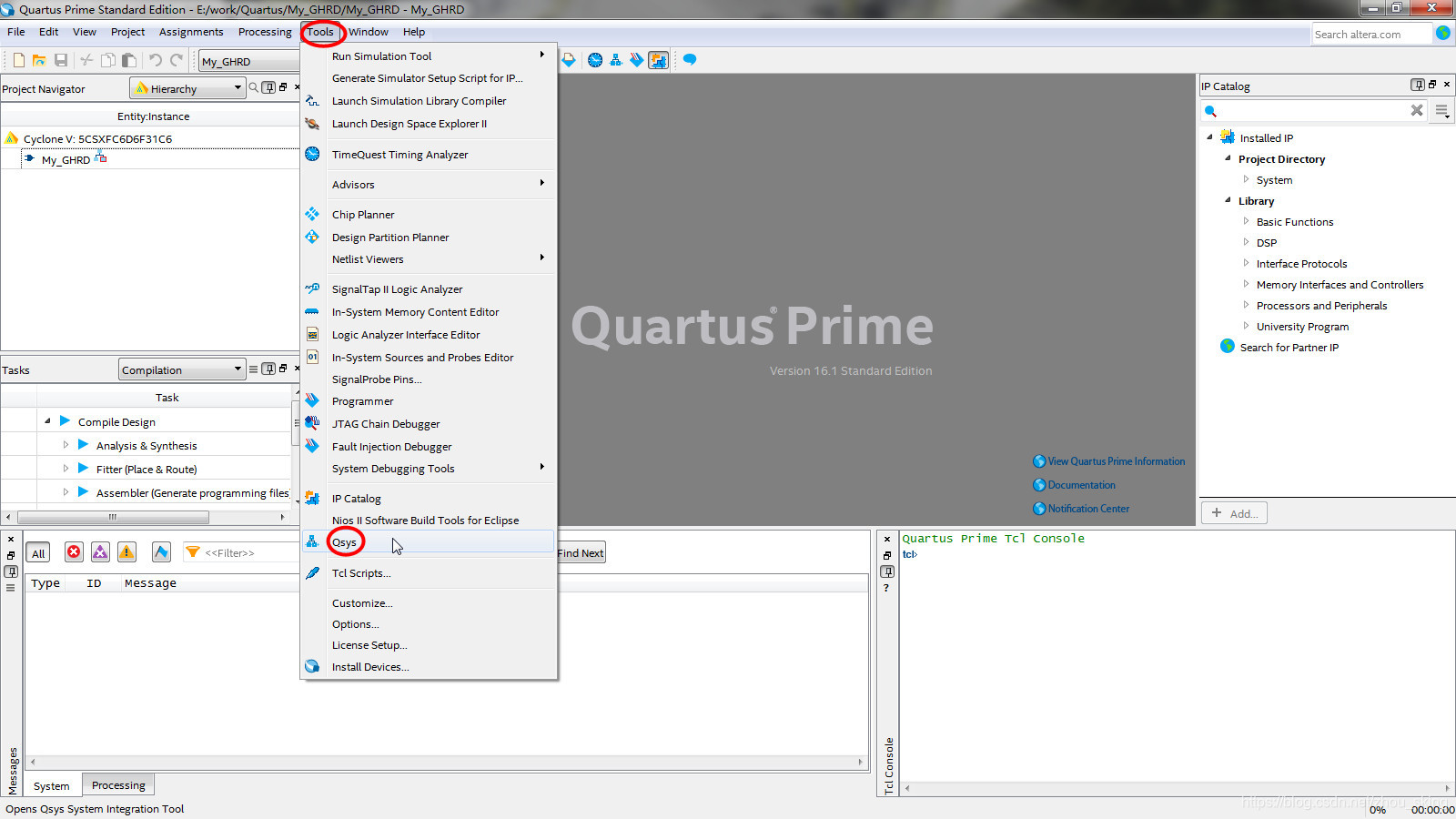

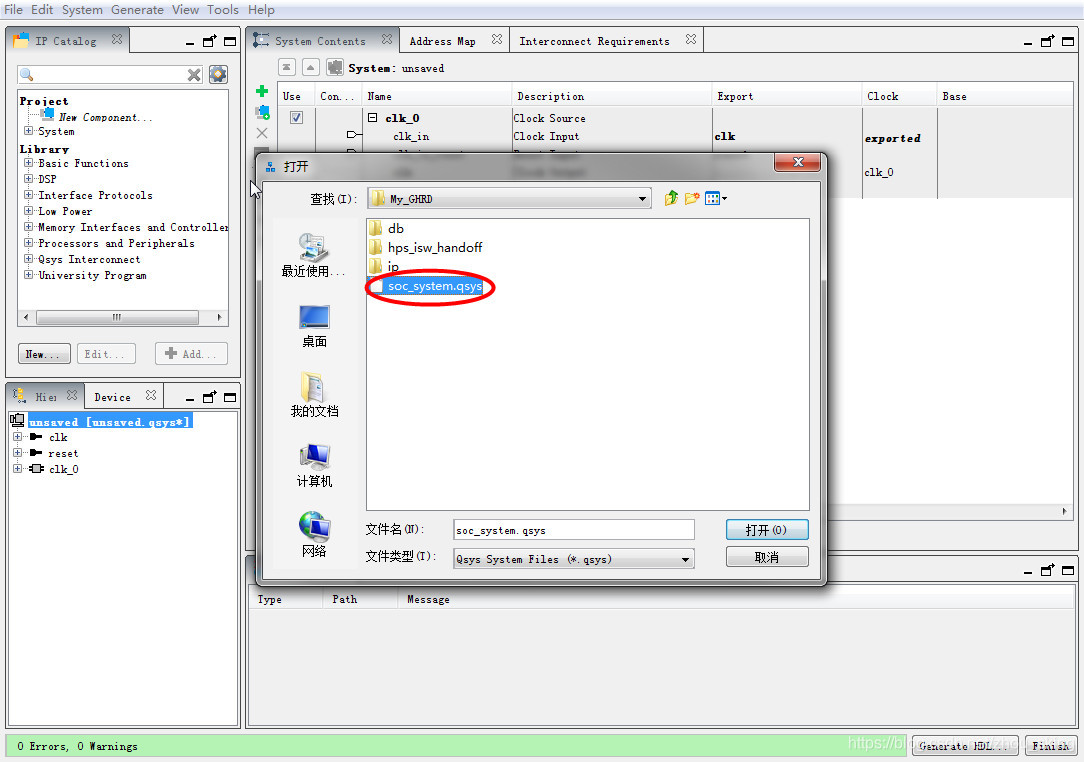

依次点击:Tools→Qsys,启动Qsys,之后选中要打开的soc_system.qsys文件。

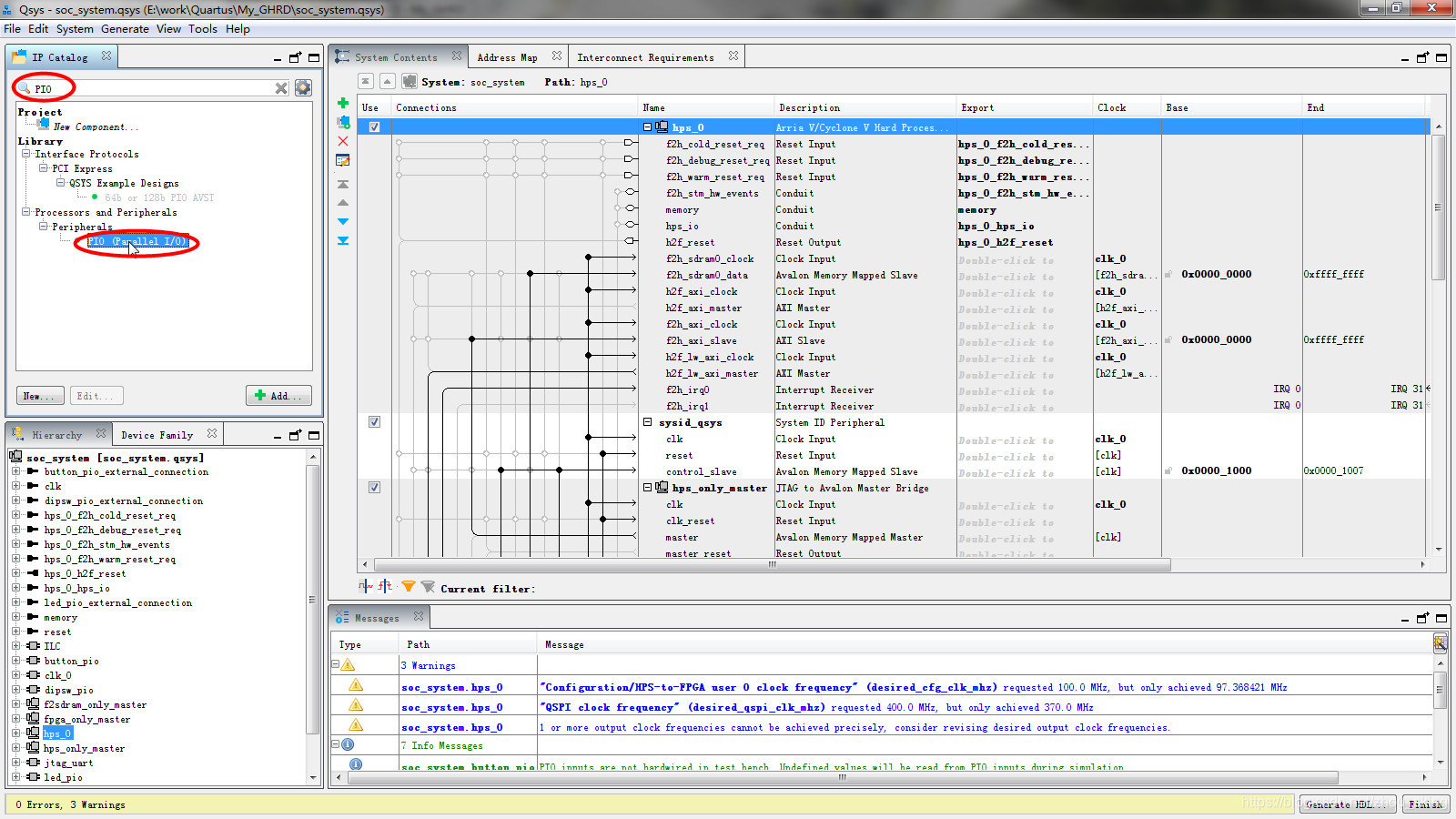

接下来,在打开的soc_system.qsys文件添加一个1位的PIO端口。在左上角的IP Catalog的搜索框中搜索“ PIO ”,之后双击下面列表中的“ PIO(Parallel I/O) ”。

此时将弹出“ PIO(Parallel I/O) ”设置界面。将PIO的数据宽度Width设置为:1,数据输入输出方向Direction设置为:Output。最后点击右下角的Finish按钮退出设置。

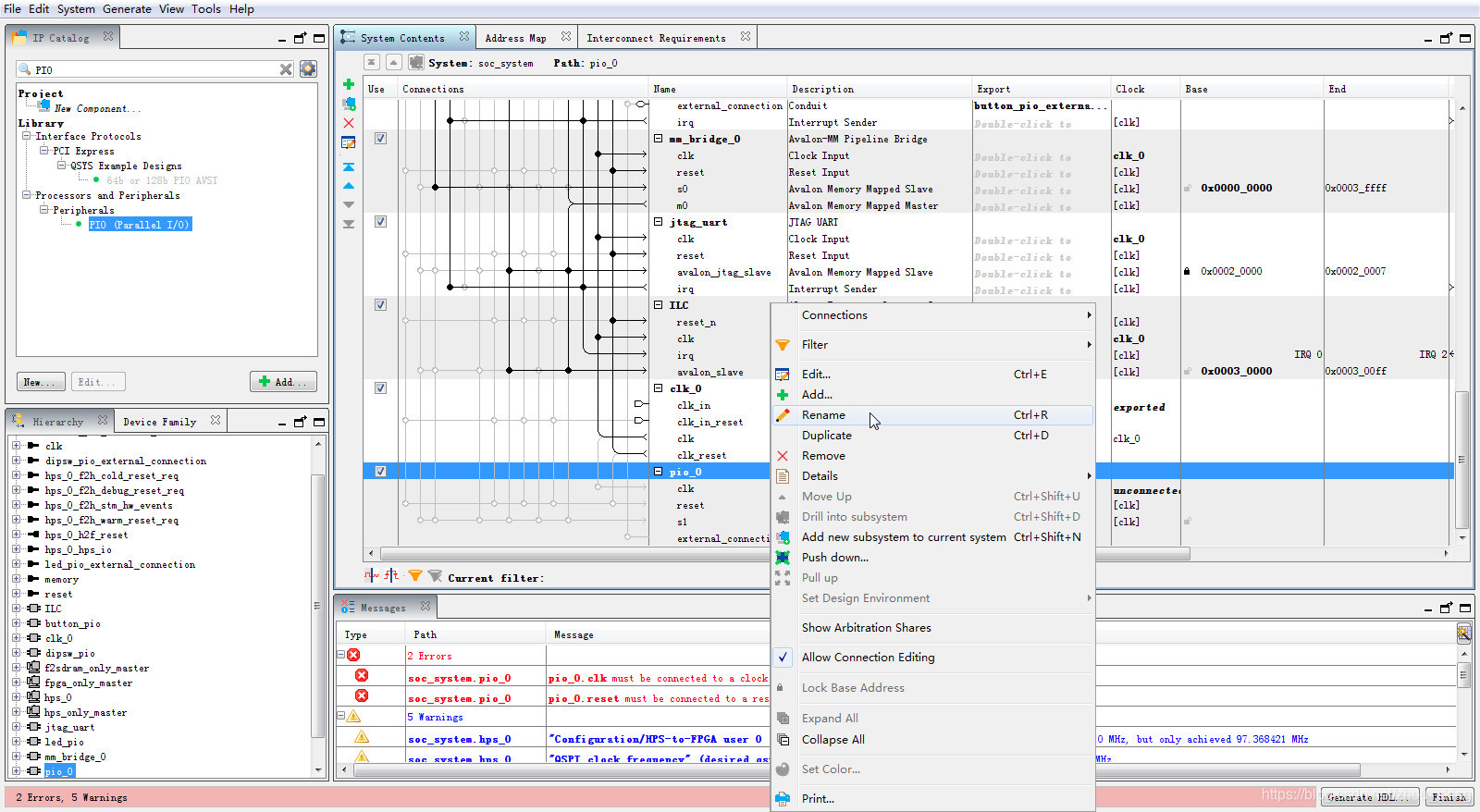

现在,新的Qsys设计中将会出现我们新添加的PIO端口pio_0,我们可以对其进行重命名。光标移动到在端口名pio_0处,右键选择“Rename”,重命名为:led_pio9。点击空白处保存命名。

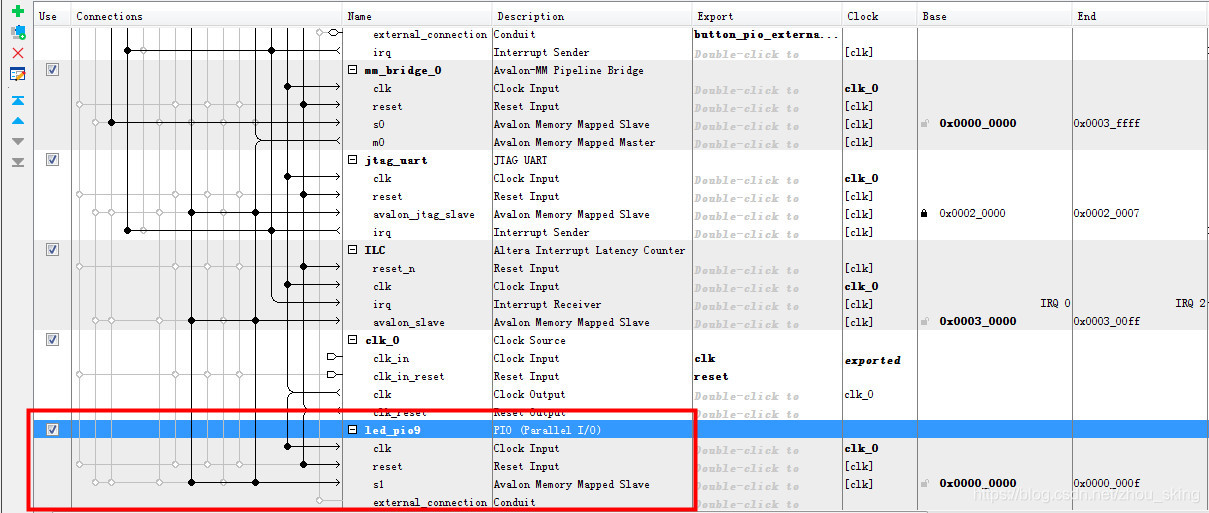

之后我们需要对led_pio9组件的信号进行连接,将光标放置到下图中led_pio9组件中clk信号所在行的白点处,点击后可以将led_pio9组件中clk信号与clk_0组件的clk信号进行连接,可以表示为:led_pio9.clk—clk_0.clk。使用类似的操作,将led_pio9组件的其它信号分别与其它组件进行如下连接,最终的连接关系如下:

- led_pio9.clk—clk_0.clk

- led_pio9.reset—clk_0.clk_reset

- led_pio9.s1—mm_bridge_0.m0—fpga_only_master.master

如下图:

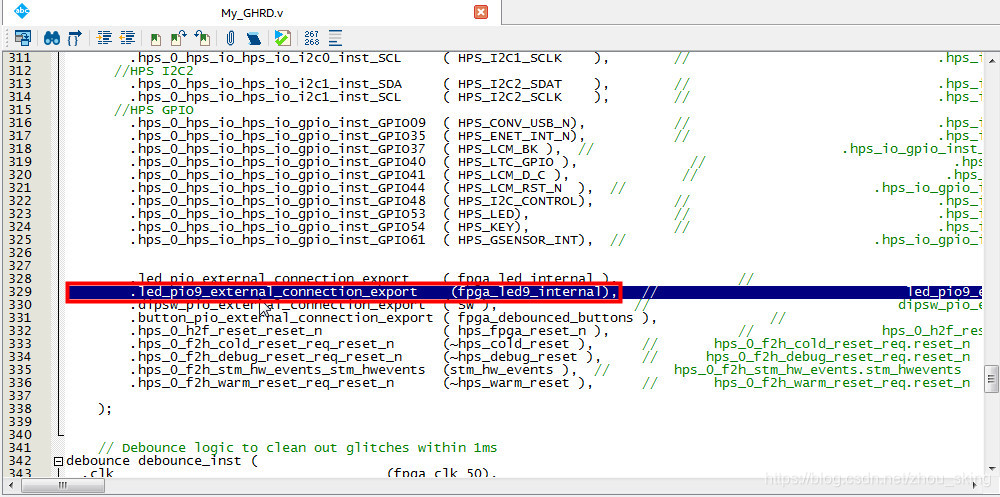

其中led_pio9有一个信号led_pio9.external_connection需要进行对外引出。光标置于信号led_pio9.external_connection处右击选择:Connections:led_pio9.external_connection→Export as: led_pio9_external_connection。

到此,添加一个1位的PIO端口led_pio9的操作已经完成。

接下来需要将原来控制LEDR0-9的数据宽度为10位的PIO端口led_pio更改为只用控制LEDR0-8的数据宽度为9位的PIO端口led_pio。双击组件led_pio,将数据宽度Width(1-32 bits)设置为:9,关闭Parameters窗口将自动保存更改。

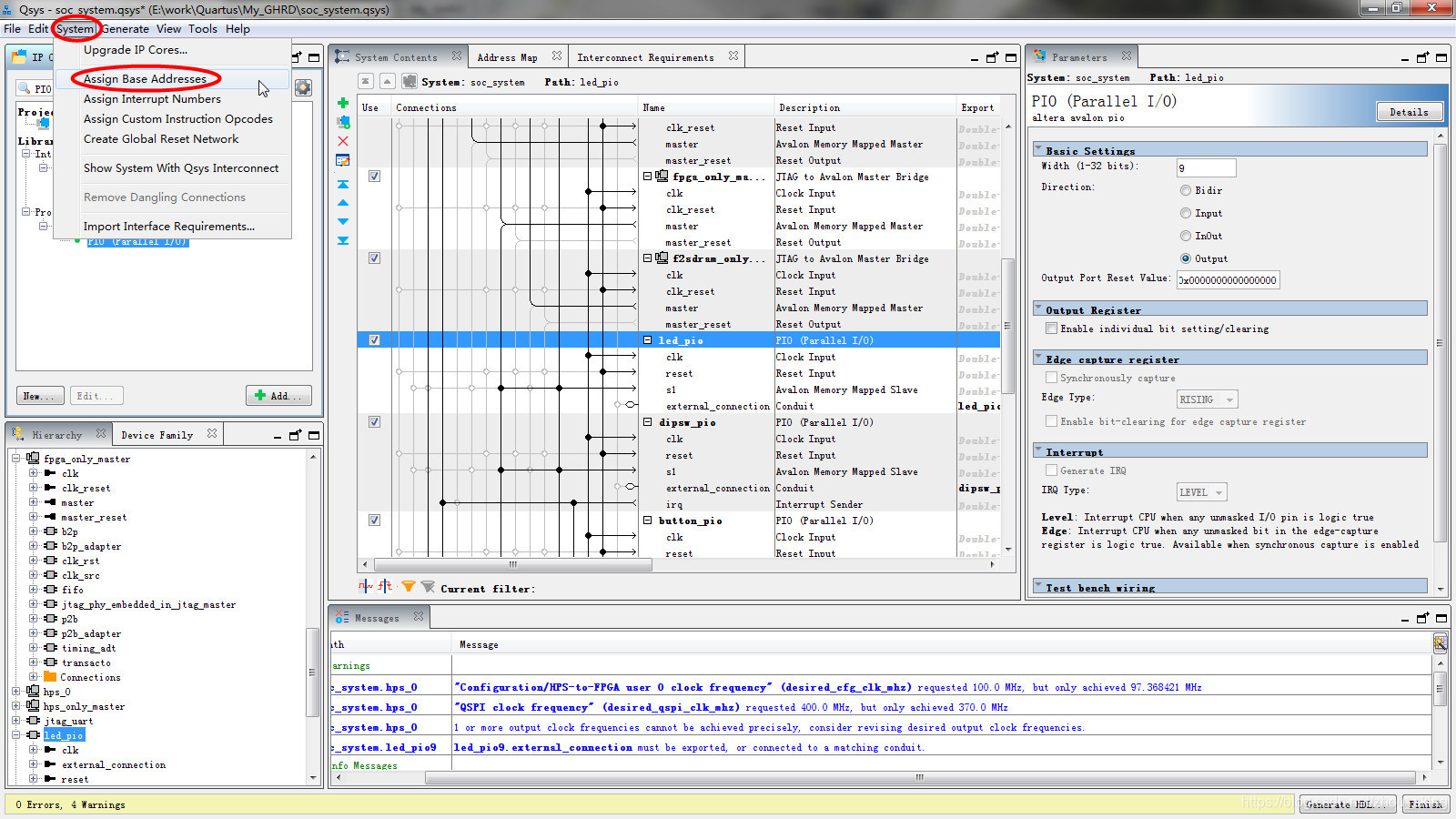

现在,我们要为我们新添加的PIO端口led_pio9分配基地址,同时更新Qsys设计中其它组件的基地址。依次点击:System→Assign Base Addresses。

可以看出,至此,我们需要在Qsys设计中做的更改已经完成了。现在,只要重新生成相应的HDL文件,更新Qsys设计就可以结束Qsys部分的设计了。但是后面对工程编译时软件将会输出错误提示:

Error (10228): Verilog HDL error at soc_system_sysid_qsys.v(34): module “soc_system_sysid_qsys” cannot be declared more than once。

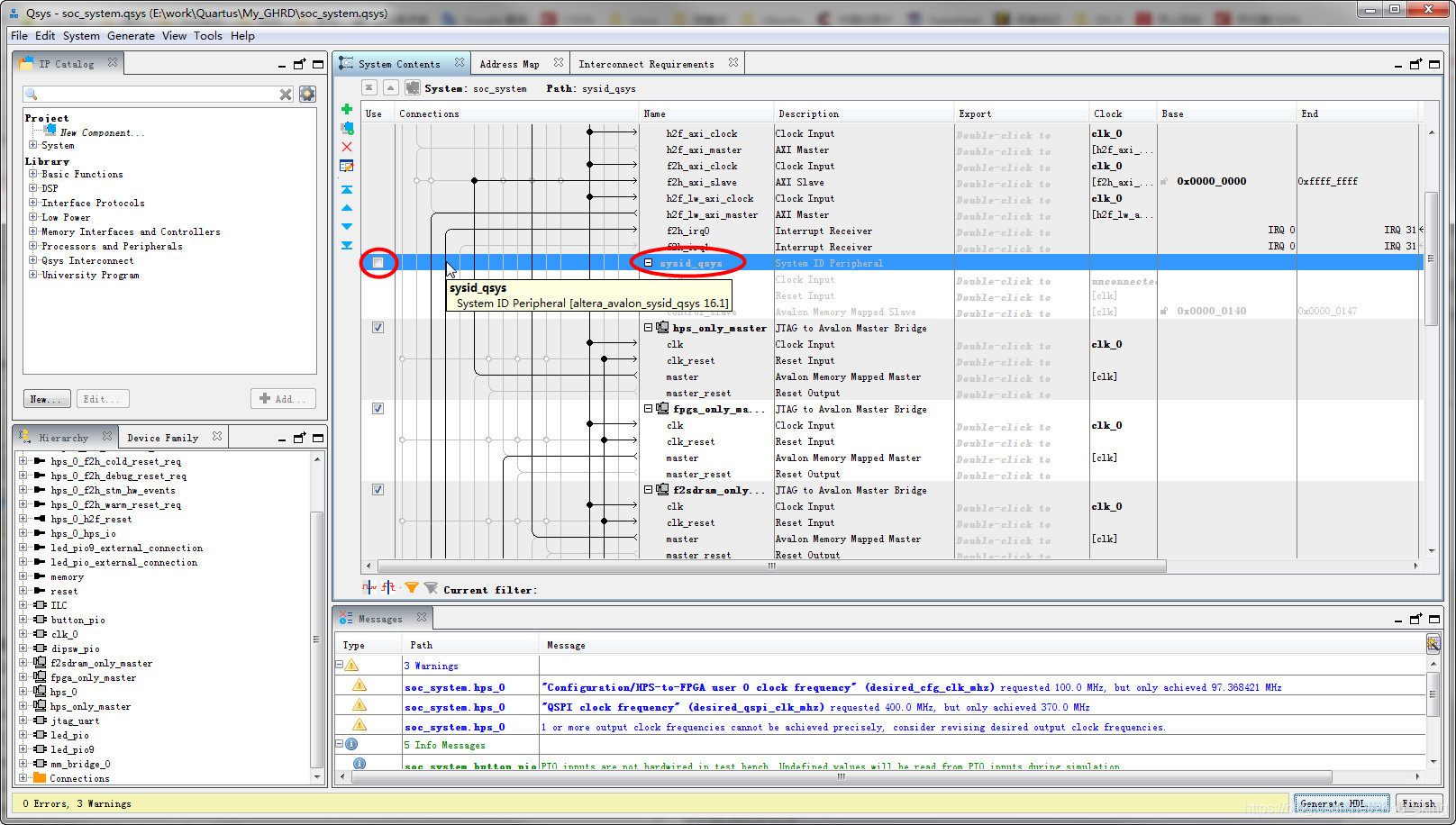

更令人遗憾的是,目前本人还没有找到解决上述错误信息的办法。有一个无奈的办法就是:将Qsys设计中的soc_system_sysid_qsys组件删除。这不会影响Qsys设计的功能,关于该组件功能的详细介绍,读者可以自行查找,此处不再赘述。

删除soc_system_sysid_qsys组件的办法是:将soc_system_sysid_qsys组件sysid_qsys的Use列方框中的“√”去掉。

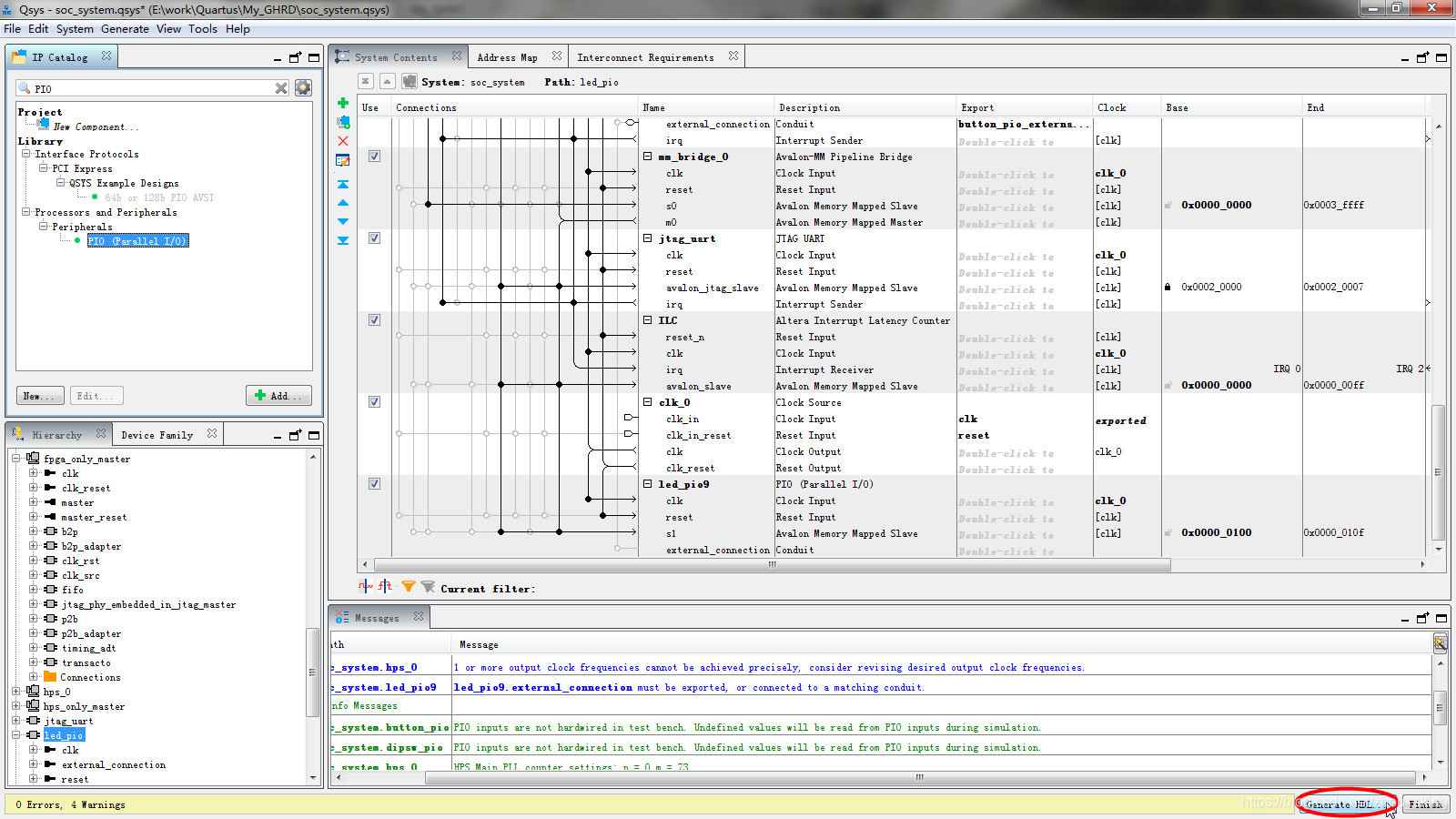

之后进行Qsys设计中的文件生成工作。点击右下角的Generate HDL…按钮。

在弹出的“Generation”窗口中,确认Output Directory下Path所指定的生成文件的输出目录在工程目录下。然后点击Generate按钮。

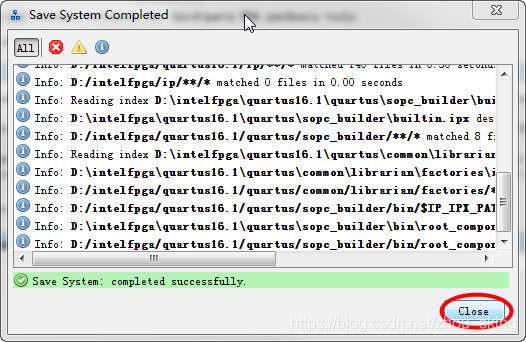

接下来会弹出“Save System Completed”窗口,点击右下角的Close按钮。

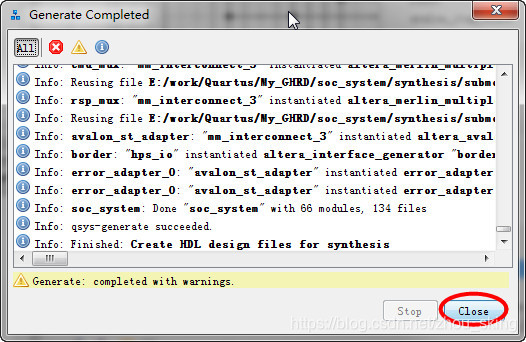

接下来会弹出的“Generate”窗口,等待几分钟,文件生成工作完成后,右下角的“Close”按钮会高亮显示。此时,点击“Close”按钮。

最后,又会退回到Qsys设计页面,点击右下角的Finish按钮,退出Qsys设计。

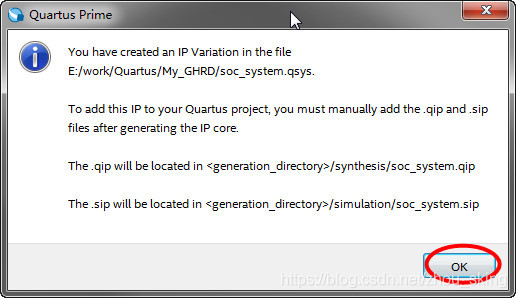

在返回Quartus Prime Standard Edition主界面后,会提示我们把更新后的.qip和.sip文件重新手动添加到工程中来。点击提示窗口右下角的Close按钮。

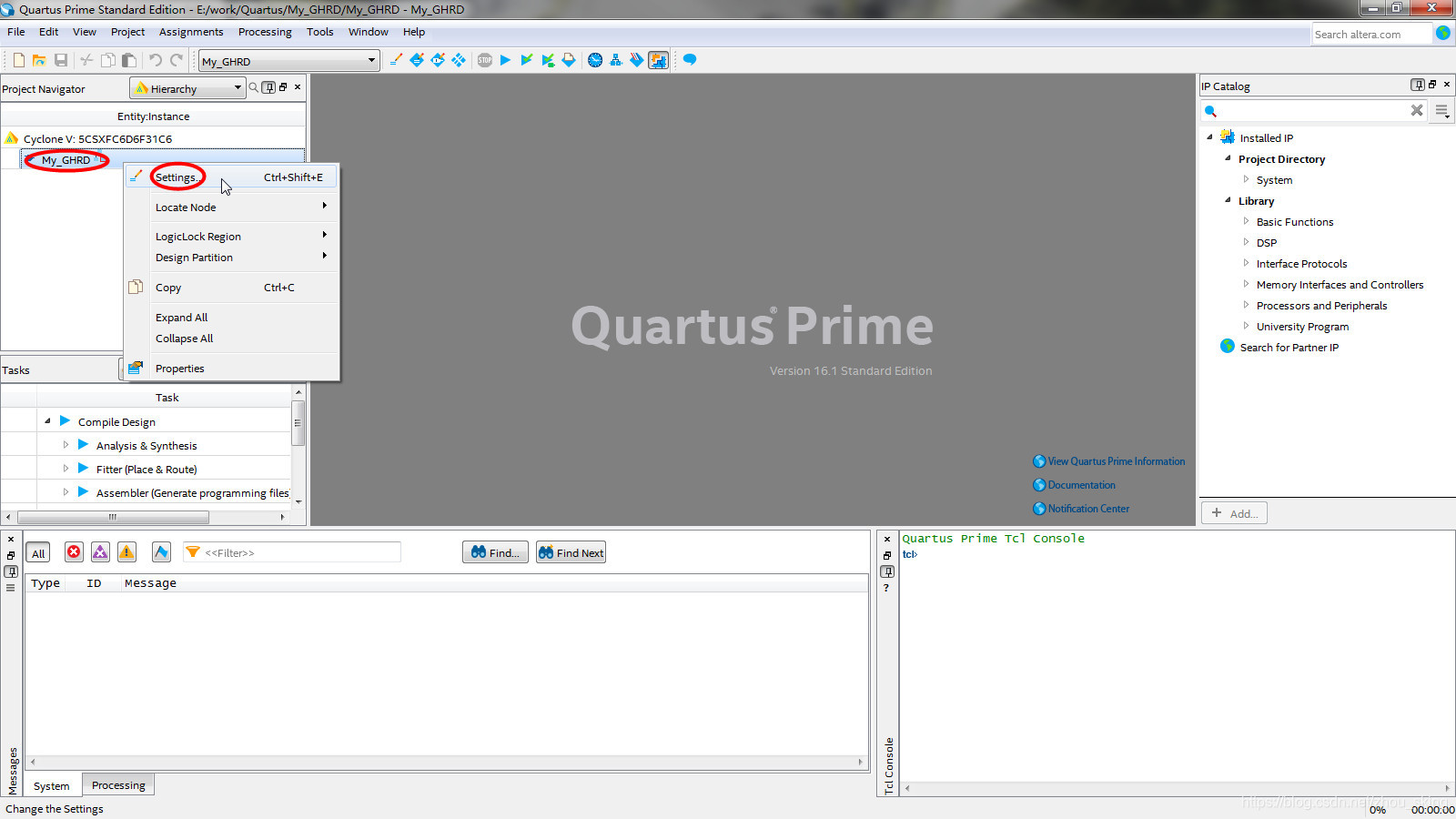

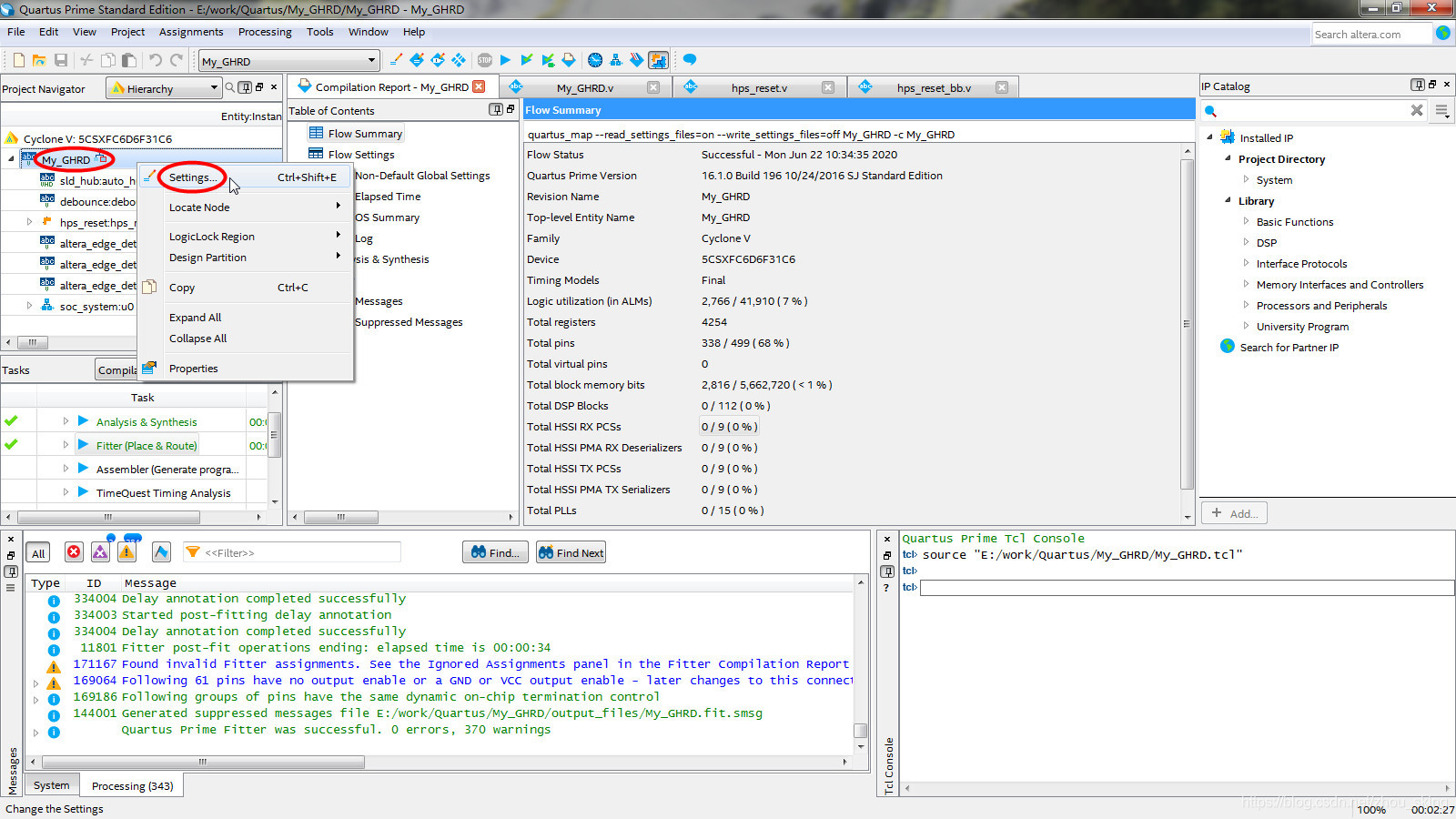

现在,我们来手动添加更新后的.qip和.sip文件。右击Project Navigator窗口中工程名:My_GHRD。点击Settings…选项。

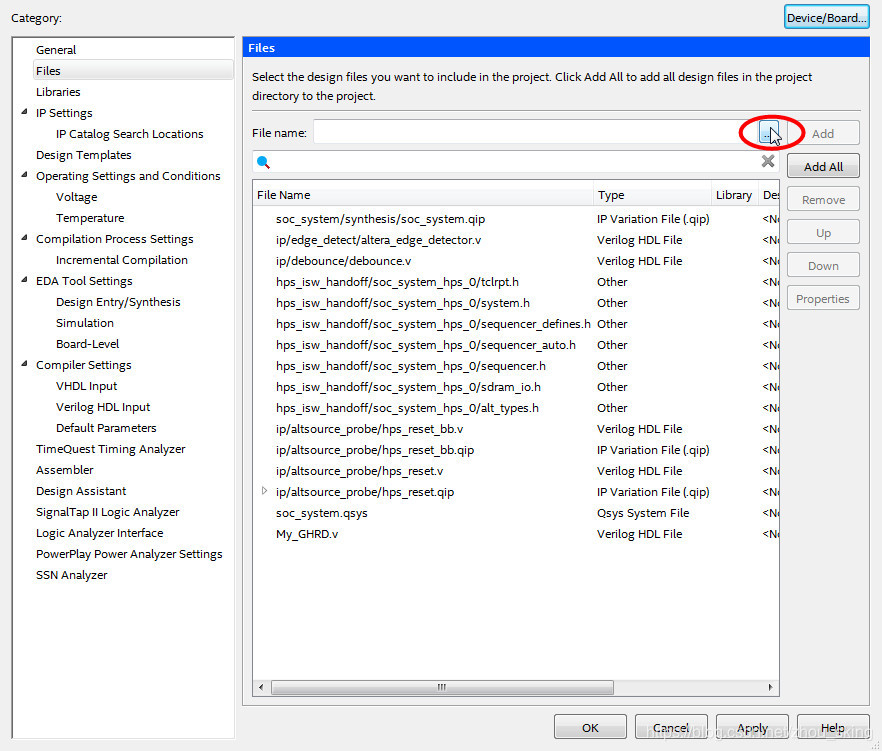

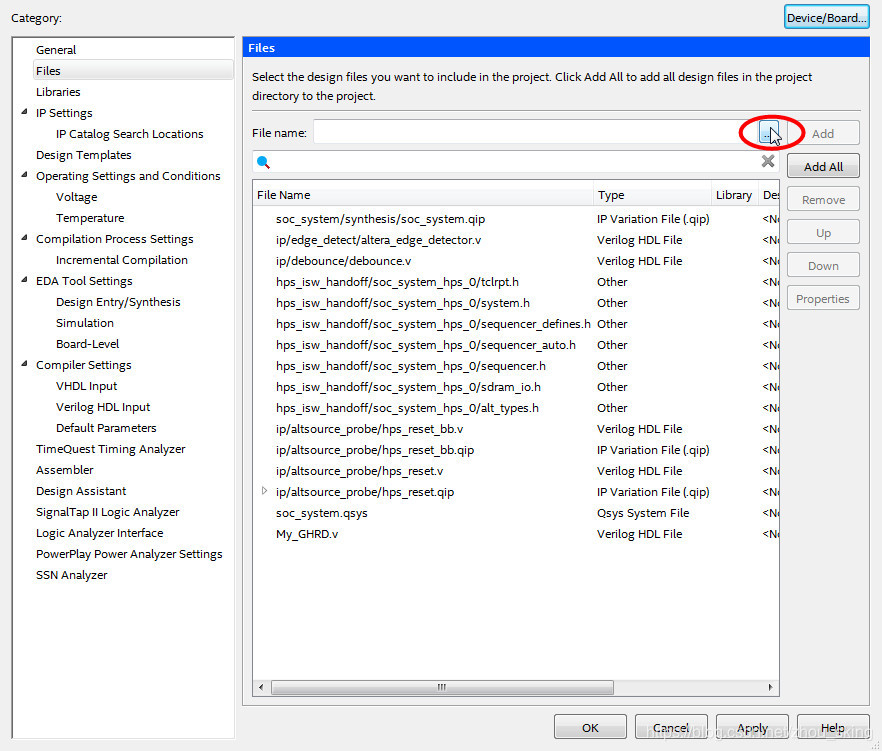

接下来会弹出Category界面,点击右侧的…按钮。

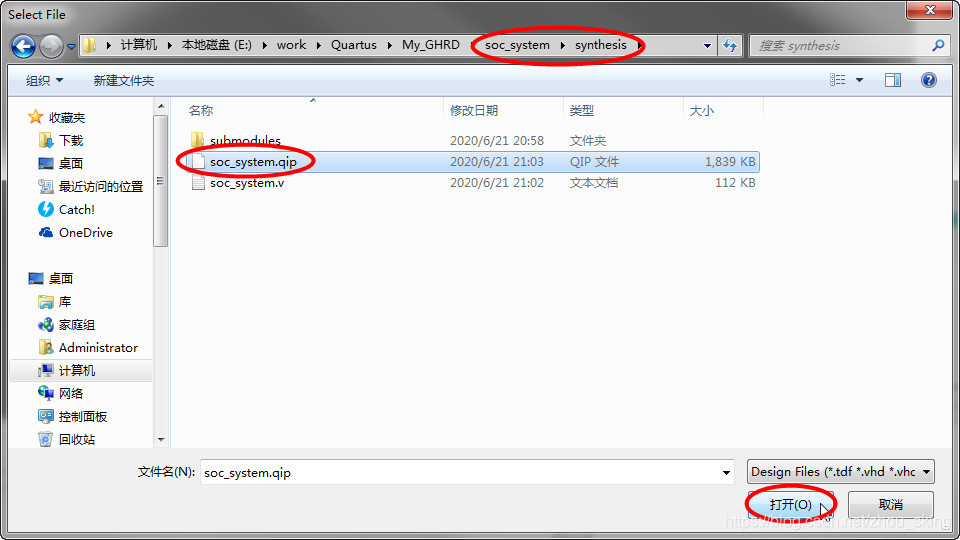

此时会弹出Select File界面,在指定的目录下找到生成的soc_system.qip文件并选中,然后点击右下角的“打开”按钮。

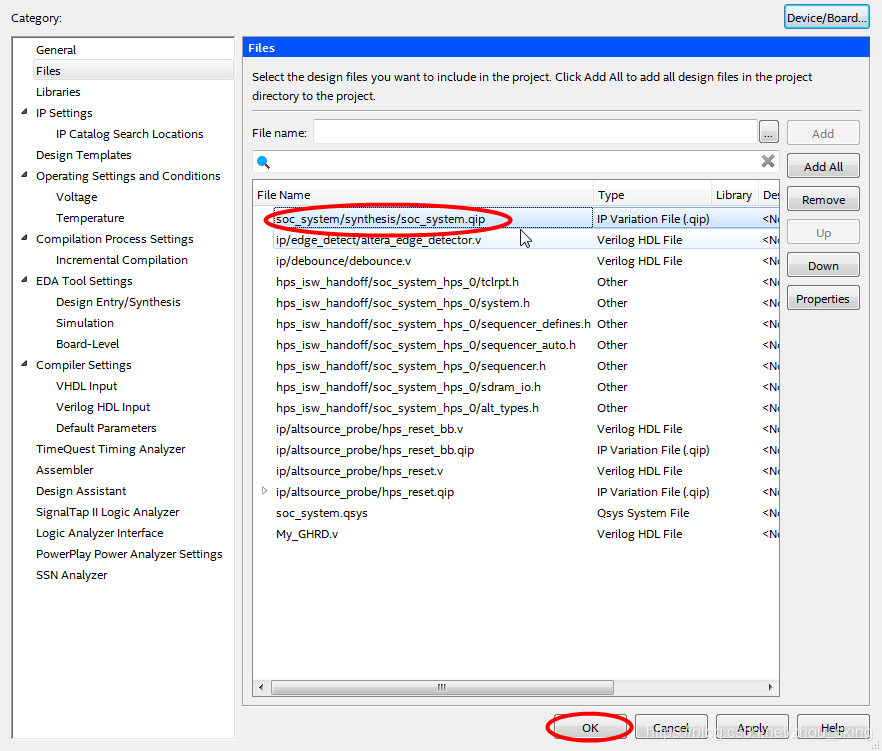

最后,可以在返回的Catagory界面中可以看到生成的soc_system.qip文件已经被成功添加到工程中。点击,右下角的OK按钮退出该界面。

至此,工程My_GHRD中Qsys部分的设计已经完成。接下来我们需要对工程中的硬件描述文件.v文件进行修改。其实,我们在DE10_Standard_GHRD工程的基础上只用对My_GHRD中顶层实体文件My_GHRD.v中各个模块的引脚及其连接关系进行描述即可。

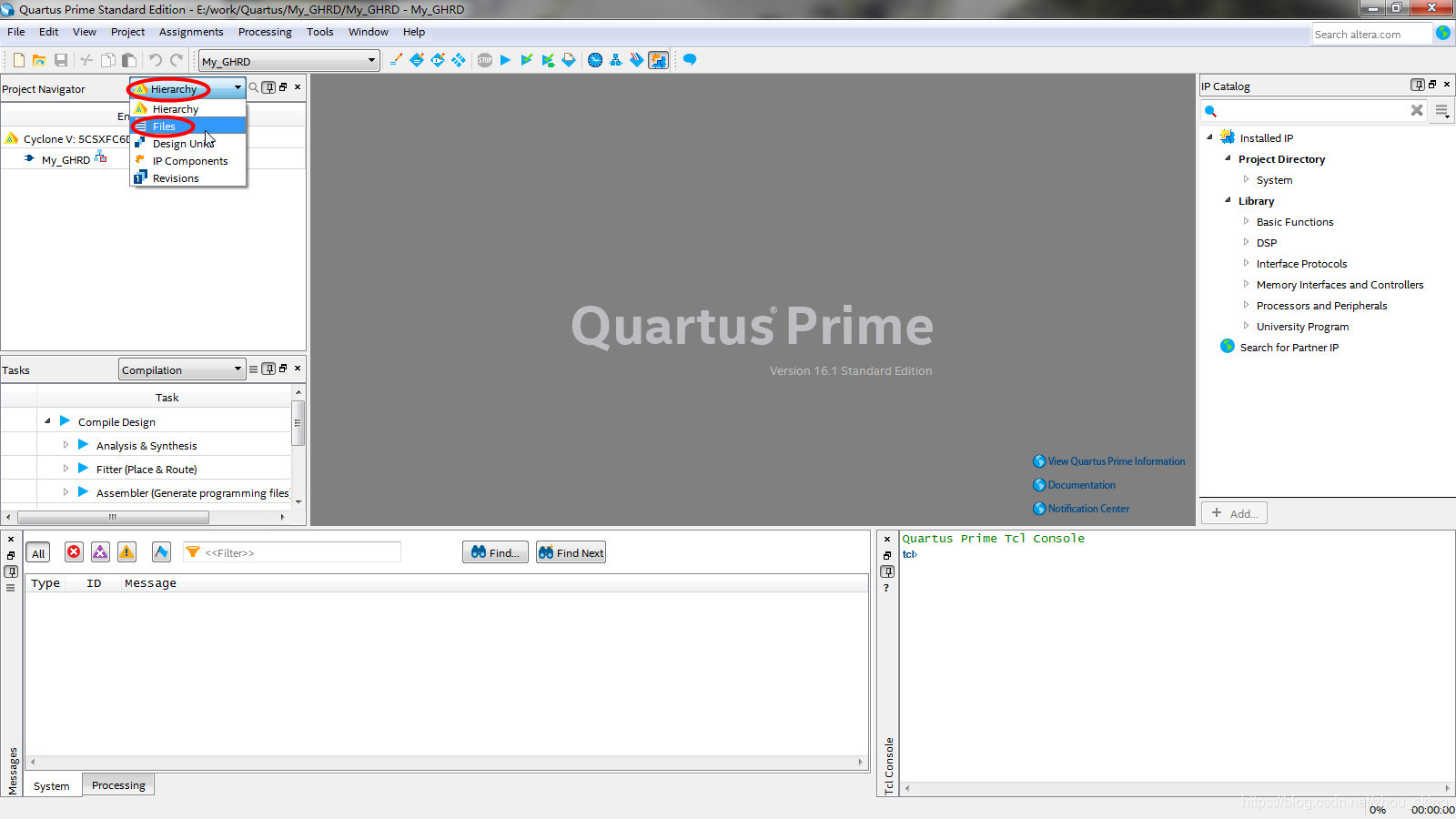

在此之前,我们先指定我们的顶层实体文件My_GHRD.v。点击Project Navigator窗口中Hierachy按钮,会弹出下拉列表,我们点击File选项。

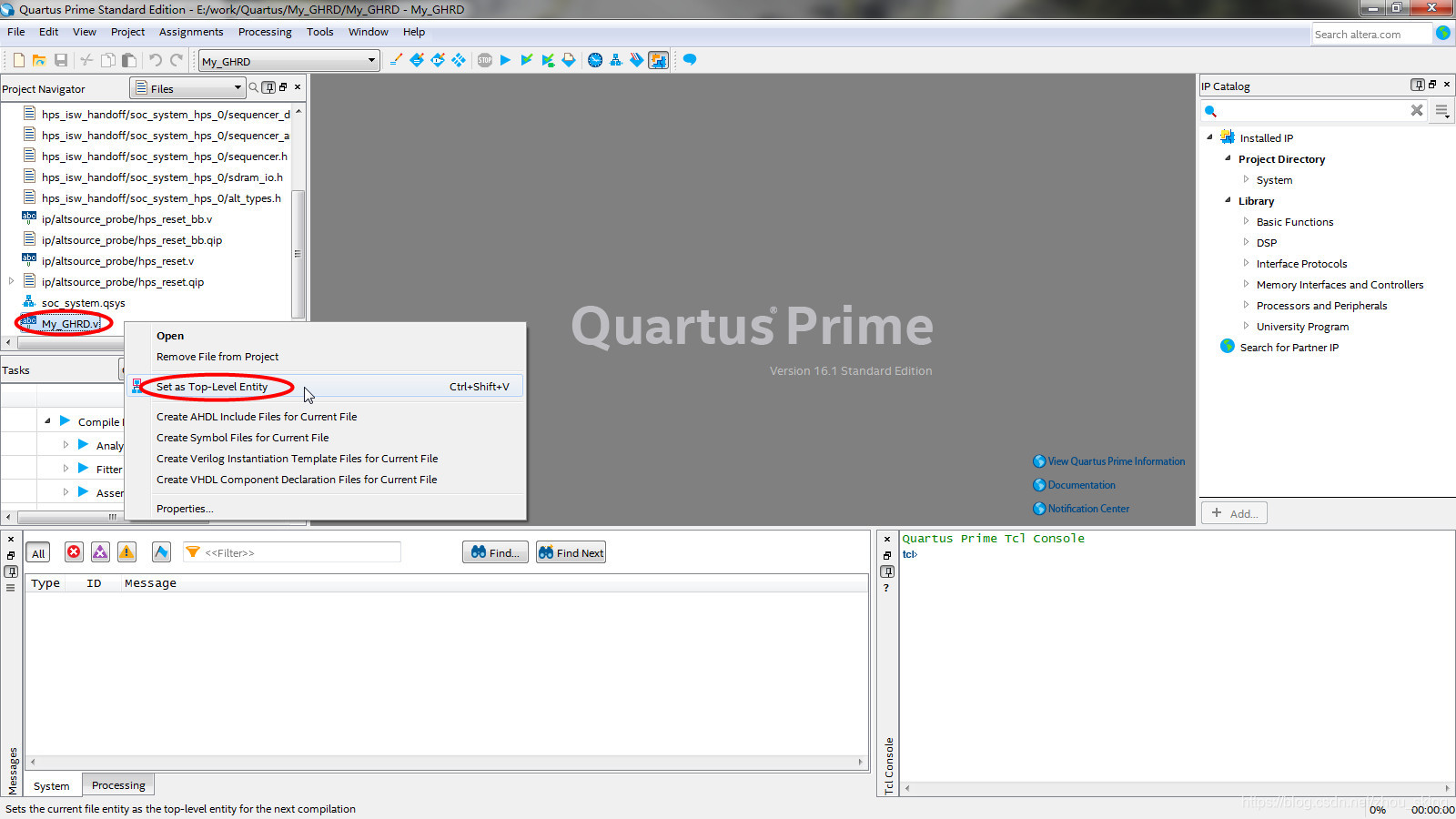

找到工程中的My_GHRD.v,右击选择Set as Top-Level Entity。

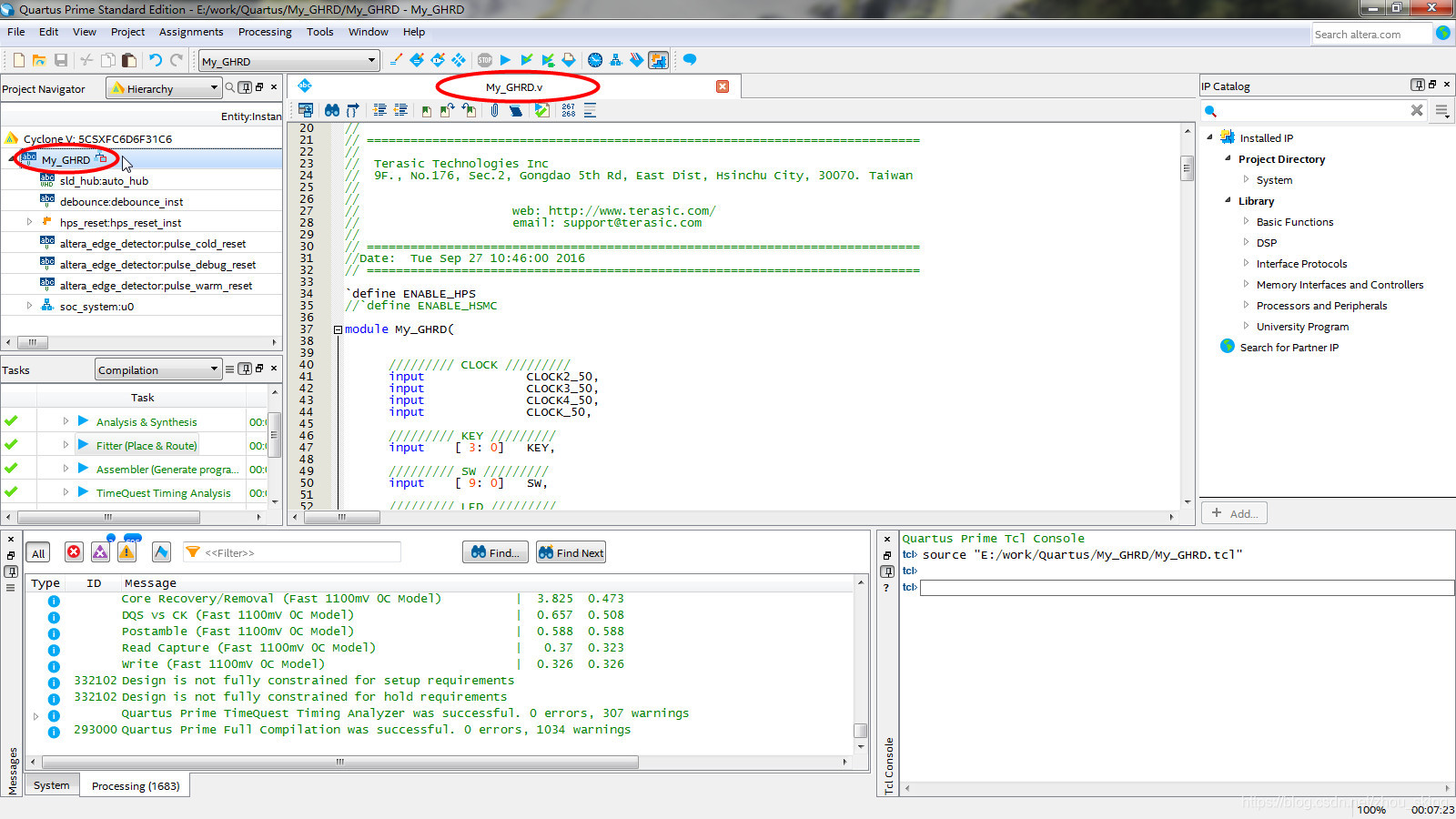

我们双击Project Navigator窗口中工程名My_GHRD,此时软件将会打开工程的顶层实体文件My_GHRD.v

硬件描述设计

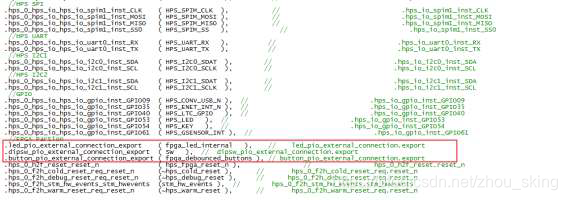

对顶层实体文件My_GHRD.v的修改主要有以下各处:

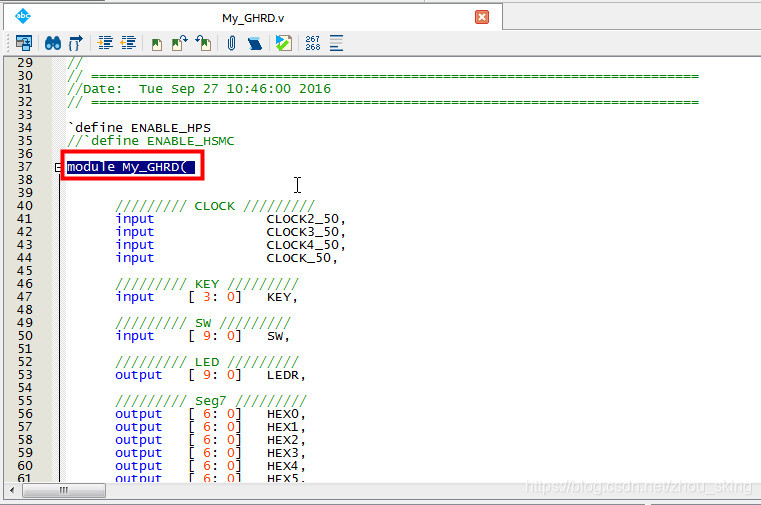

第一,顶层实体模块的命名须与工程名My_GHRD保持一致。

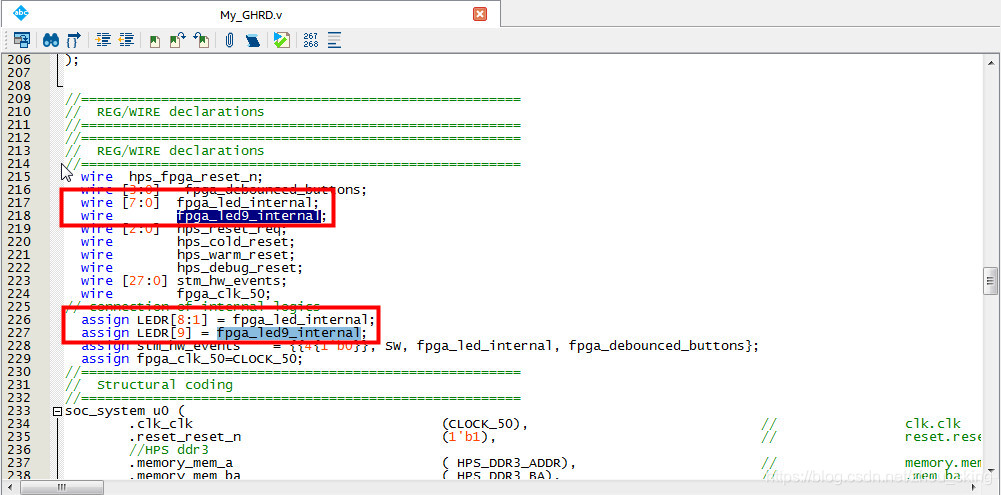

第二,在模块soc_system u0中对新引出的PIO端口led_pio9_external_connection_export进行声明。可以发现,我们声明端口led_pio9_external_connection_export的同时需要为其指定一个wire类型的变量进行连接。对照led_pio_external_connection_export连接到wire类型的变量fpga_led_internal上,我们新定义了一个wire类型的变量fpga_led9_internal与端口led_pio9_external_connection_export进行连接。当然,wire类型的变量fpga_led9_internal可以理解为是一条导线,它的一端接到了模块soc_system u0中对新引出的PIO端口led_pio9_external_connection_export上,两外一端也是要为它连接适当的端口的。我们新增端口led_pio9_external_connection_export的目的就是能够对LED灯LEDR9进行控制,所以,不难想到,wire类型的变量fpga_led9_internal另一端一定是要连接到端口LEDR[9]上面的。这样,总体的更改就是下面这样的:

- 将原来与LEDR[9:1]连接的变量wire [8:0] fpga_led_internal改为:与LEDR[8:1]连接的wire

[7:0] fpga_led_internal - 定义新的变量wire fpga_led9_internal与LEDR[9]连接

- 将新的变量wire fpga_led9_internal另一端与模块soc_system u0中的端口led_pio9_external_connection_export进行连接

My_GHRD工程编译

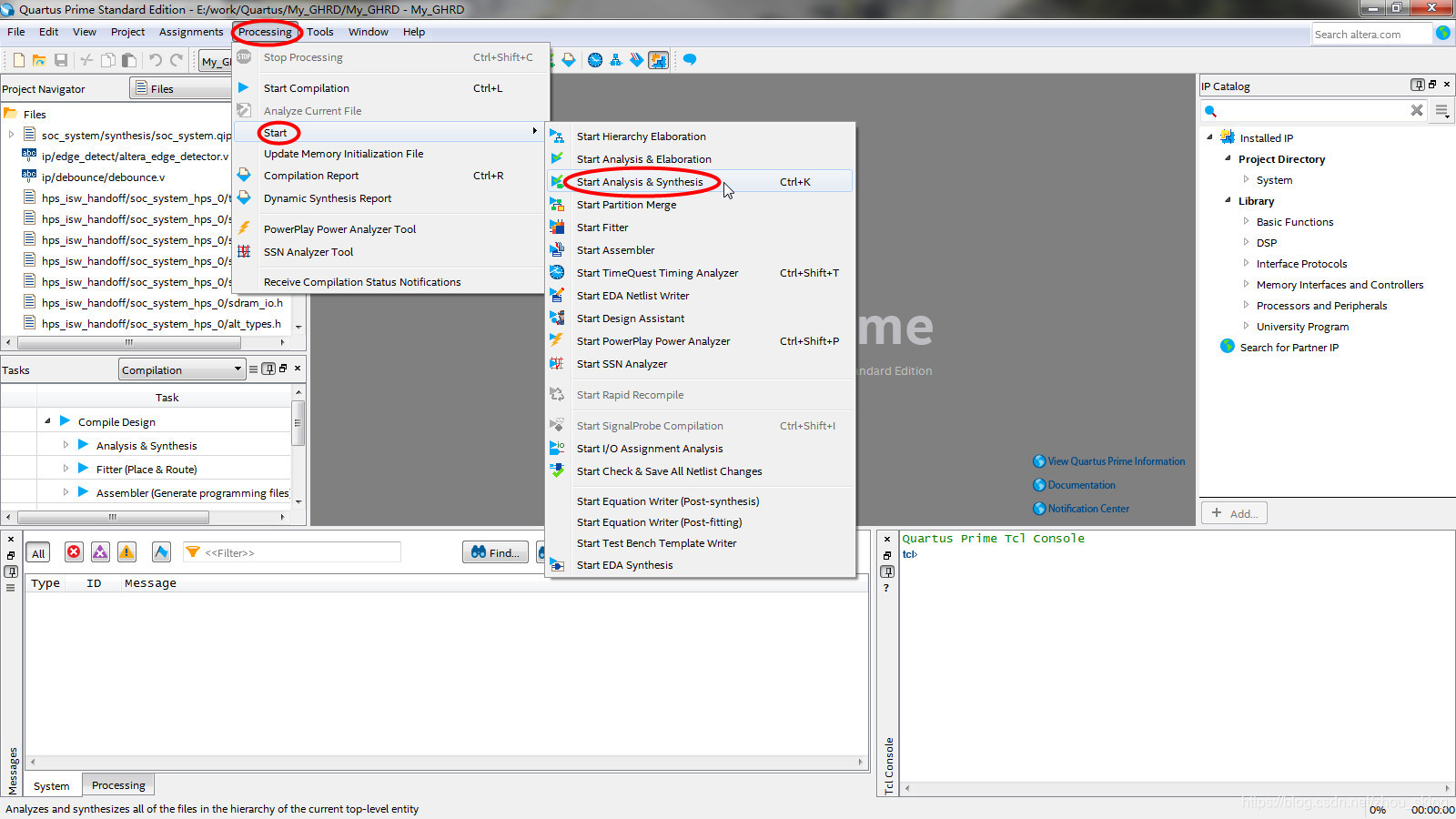

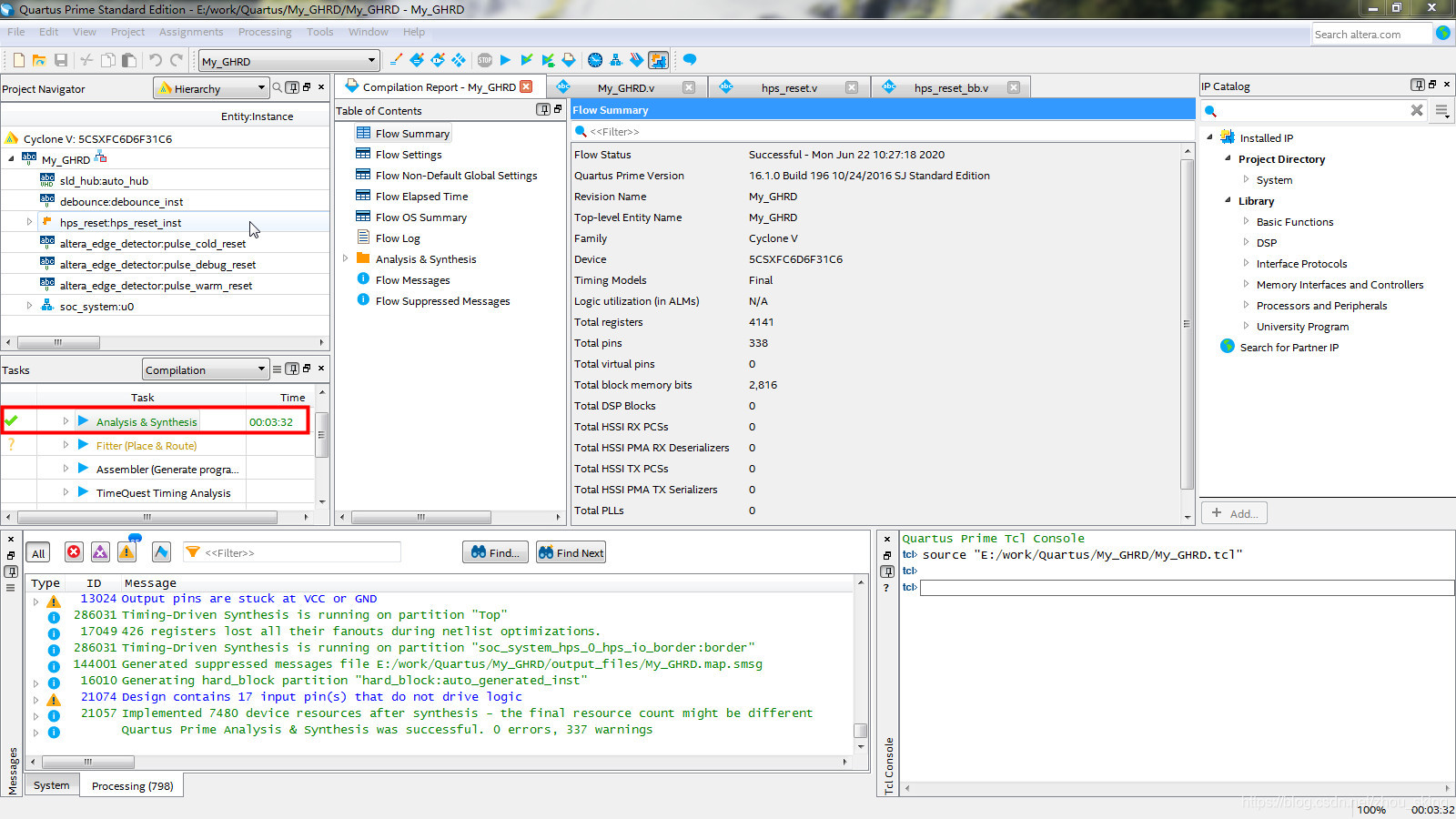

现在,我们可以对工程My_GHRD进行编译操作。首先是进行工程的分析与综合,依次点击:Processing→Start→Start Analysis & Synthesis。

工程的分析综合通过后,主界面中左侧的Tasks窗口下的Analysis & Synthesis栏前面会展示一个绿色的“√”,后面会显示分析综合所用的时间。

上面分析综合成功后,下一步需要进行Fitter(Place & Route),这里进行的是关于FPGA内部的布局布线操作。在此之前我们需要对我们模块中设计的输入输出引脚进行引脚分配。引脚分配的方法有很多种,读者可以自行学习。这里由于我们定义了大量的引脚,而且我们有现成的DE10_Standard_GHRD工程可以利用,我们只需将该工程里面的引脚分配信息转移进入我们的My_GHRD工程就可以了。

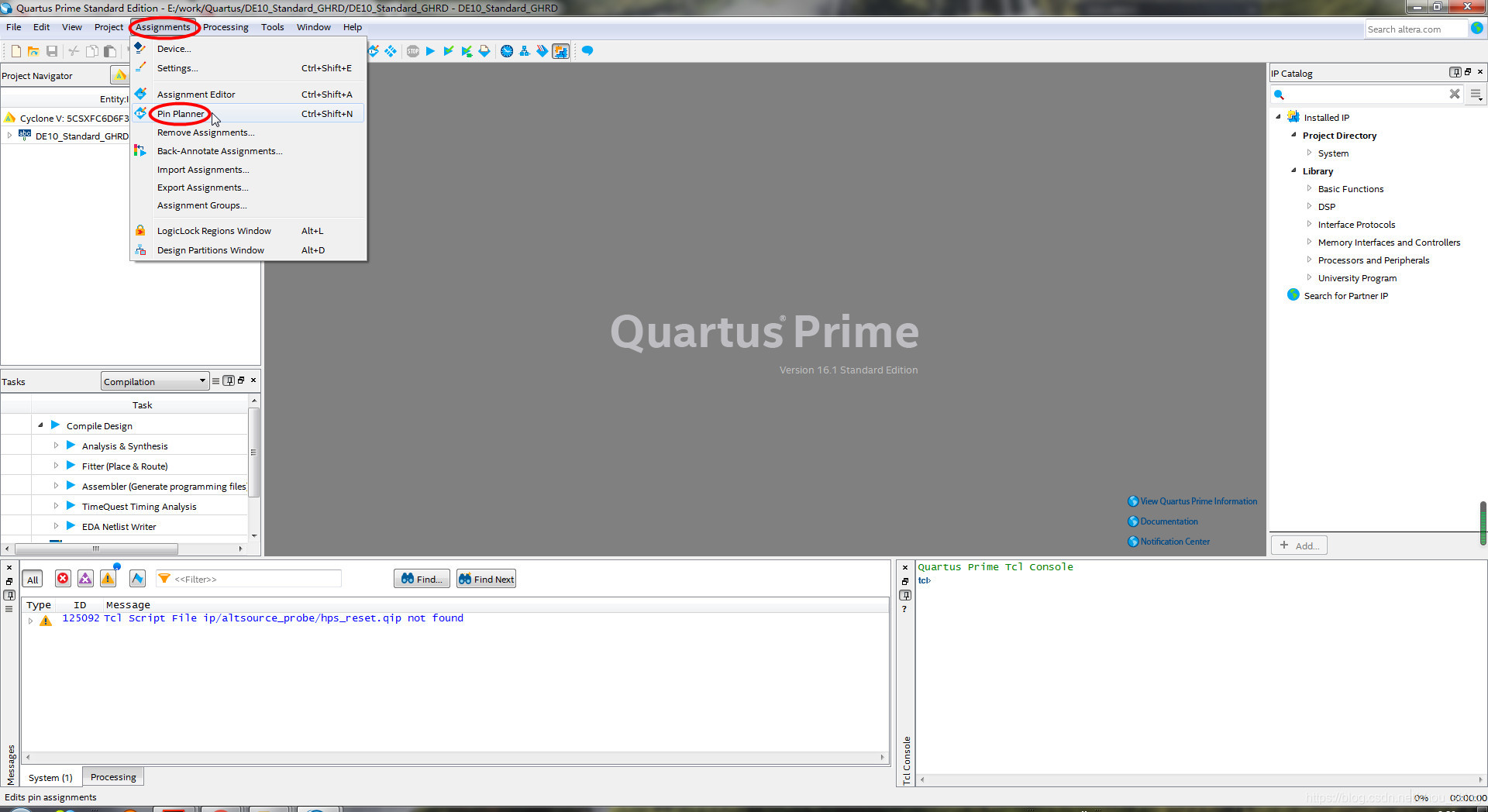

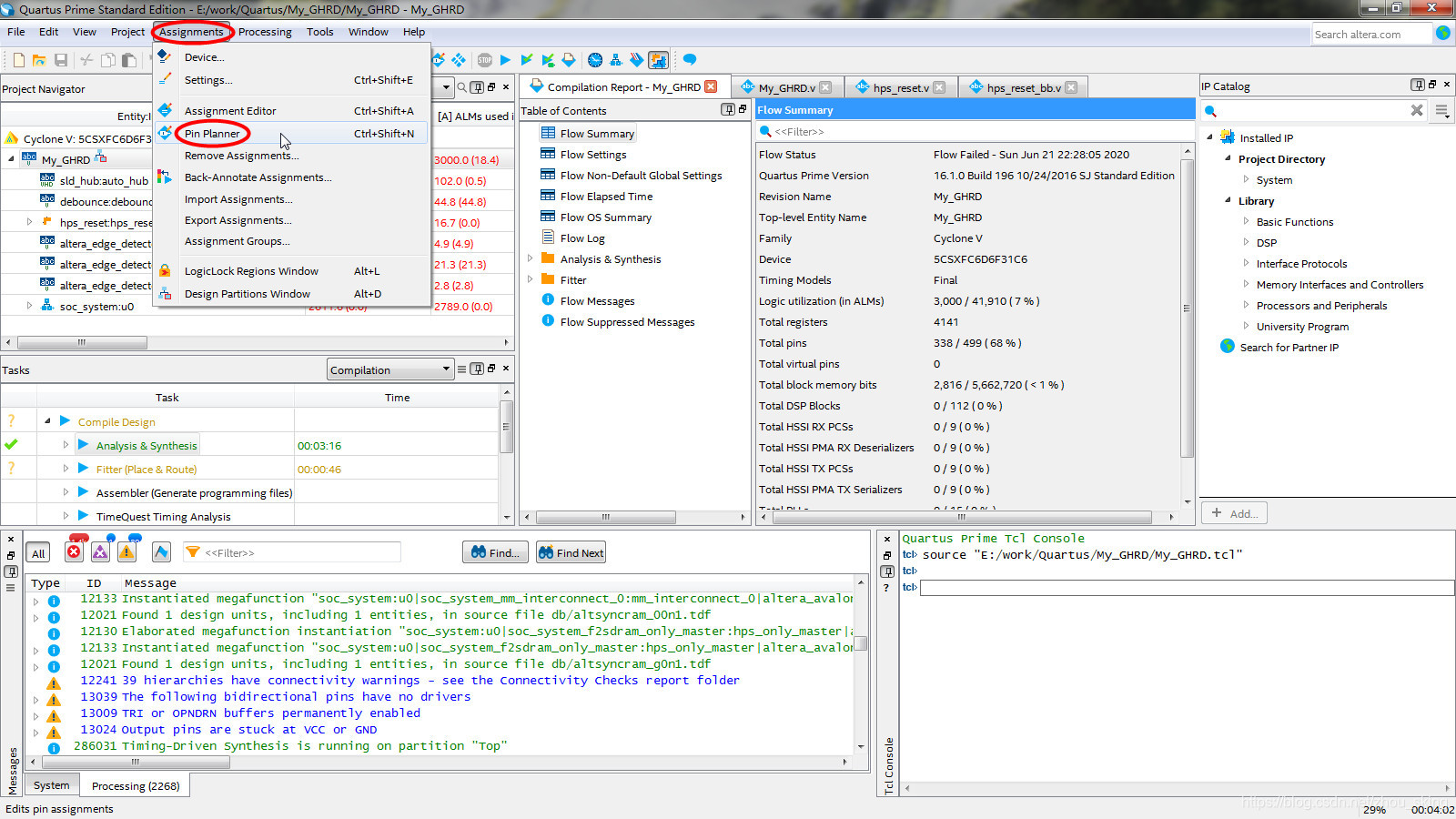

我们现在打开DE10_Standard_GHRD工程。进入工程后,我们点击:Assignments→Pin Planner,进入引脚分配界面。

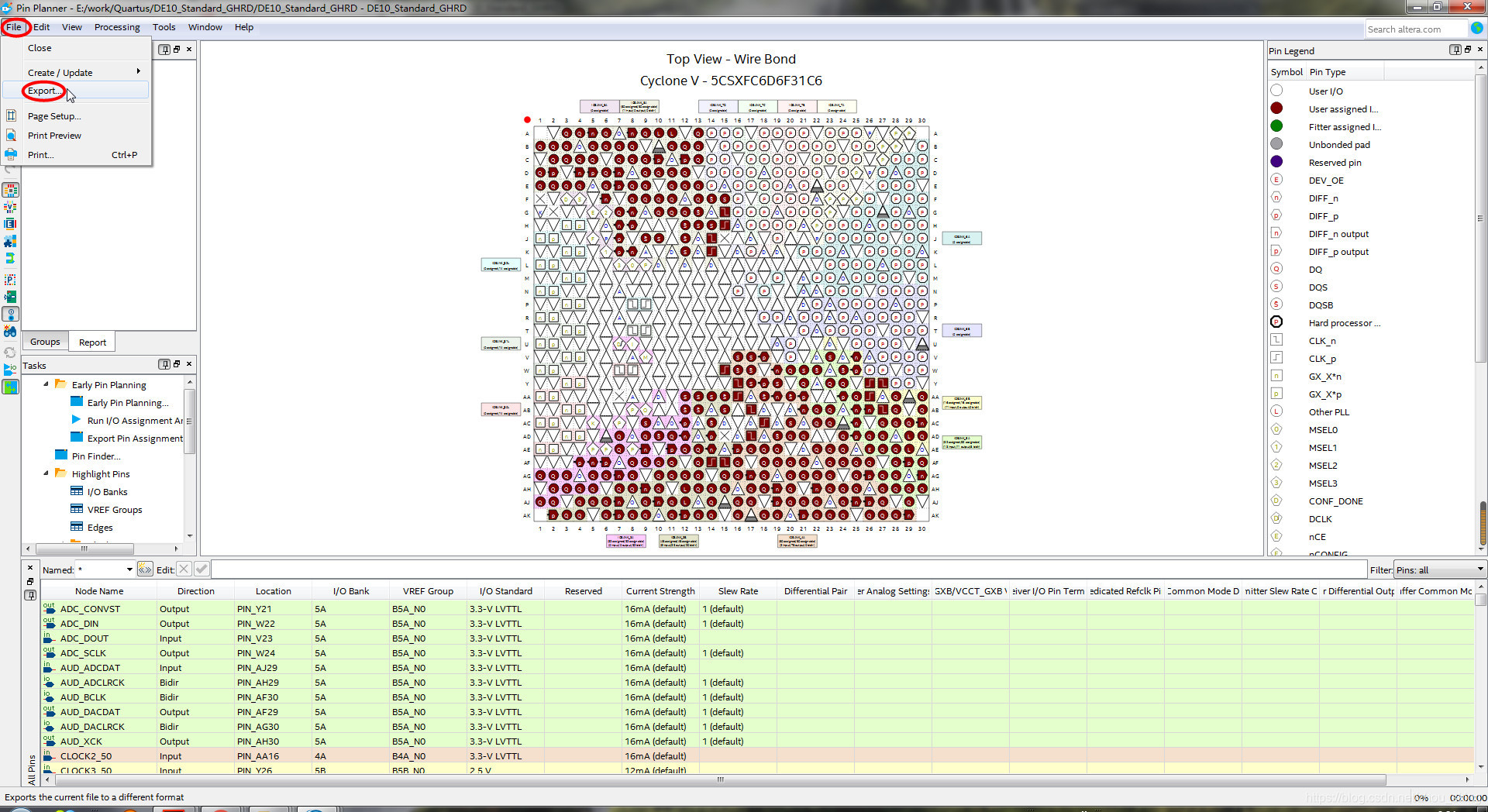

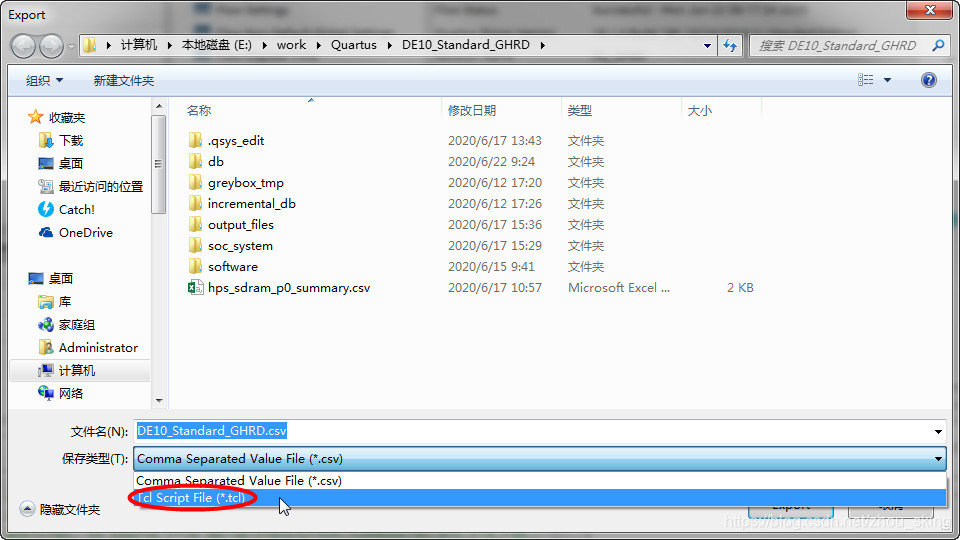

在该界面下,点击:File→Export…。

之后会弹出Export窗口。我们需要选择我们要导出的文件格式为:.tcl。

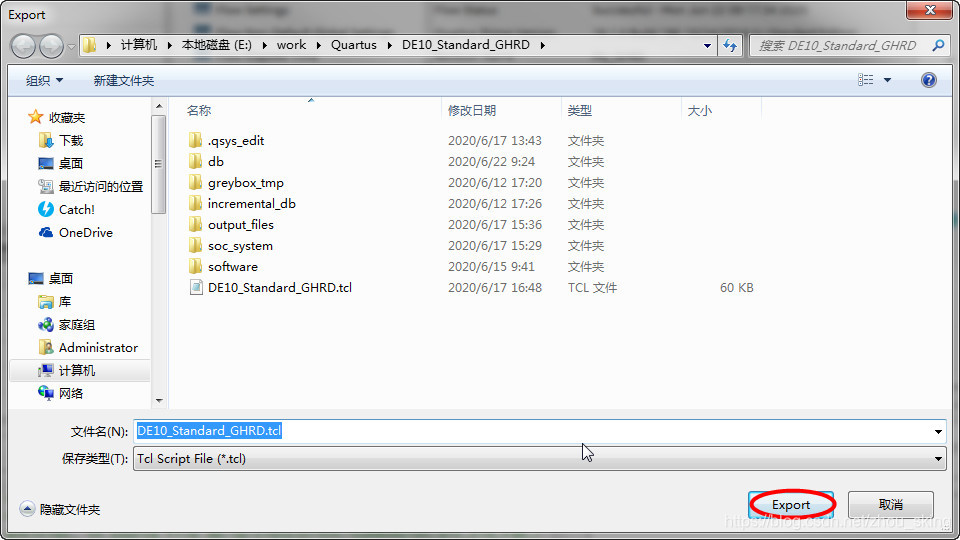

然后,点击右下角的Export按钮。

最后,依次点击引脚分配界面和DE10_Standard_GHRD工程界面右上角的关闭按钮,退出DE10_Standard_GHRD工程。

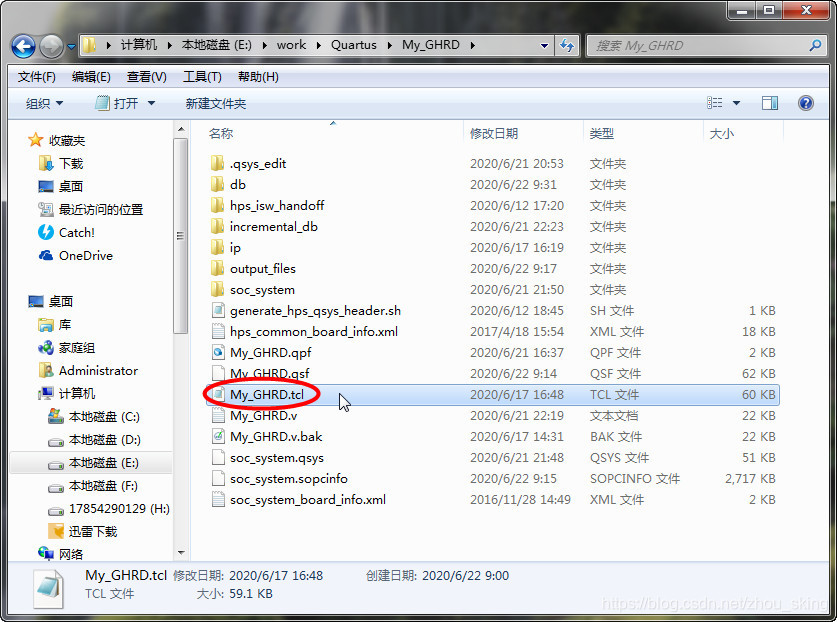

我们现在已经得到了我们需要的引脚分配文件DE10_Standard_GHRD.tcl,现在我们需要把它从DE10_Standard_GHRD工程目录下复制到My_GHRD工程目录下。为了与My_GHRD工程名保持一致,将其改名为:My_GHRD.tcl。

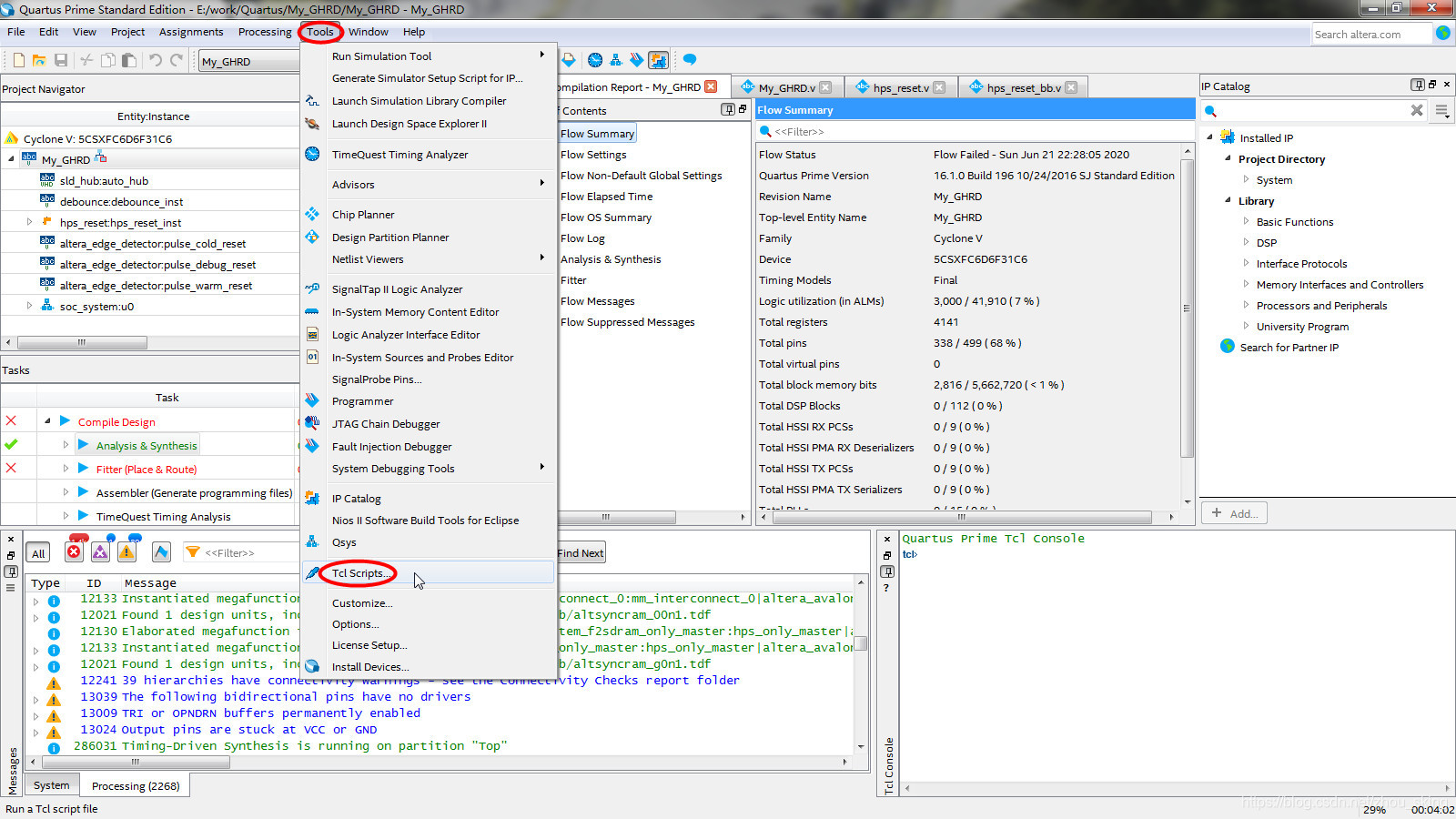

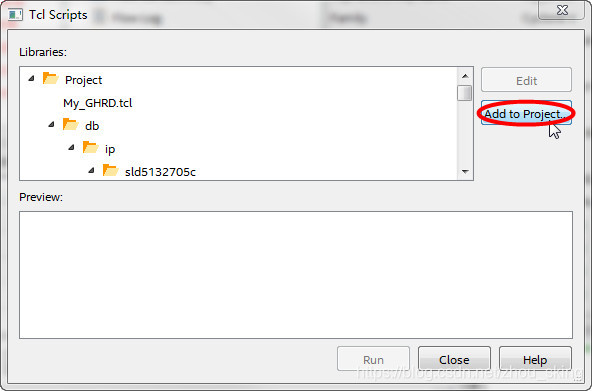

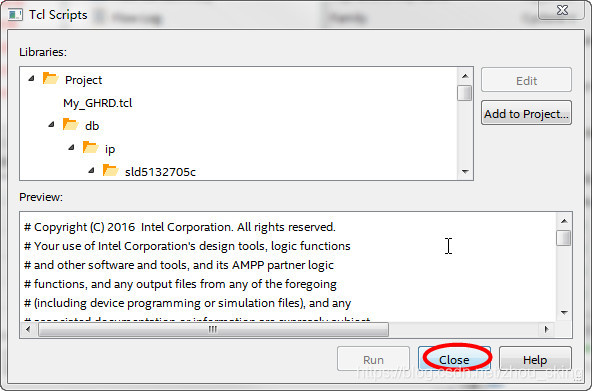

接下来,我们需要利用得到的引脚分配文件My_GHRD.tcl对工程My_GHRD中的引脚进行分配。点击:Tools→Tcl Scripts…。

在弹出的Tcl Scripts窗口下,点击右侧的Add to Project…按钮。

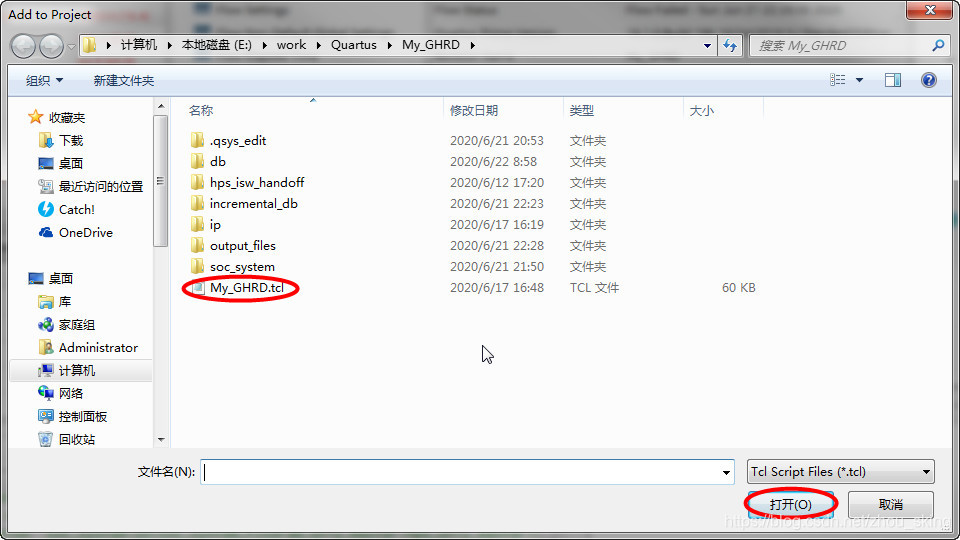

在弹出的Add to Project窗口下,选中我们的引脚分配文件My_GHRD.tcl,并点击右下角的打开按钮。

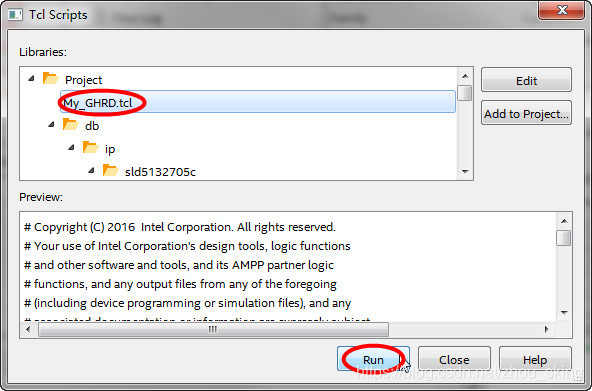

此时,软件又自动退回到Tcl Scripts窗口下。在Libraries栏中找到我们的引脚分配文件My_GHRD.tcl,点击下方的Run按钮来加载我们的引脚分配文件。

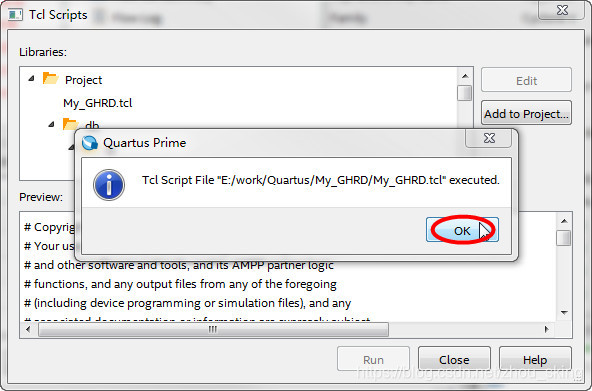

在后面弹出的界面中点击OK按钮,退回到Tcl Scripts窗口。

最后点击到Tcl Scripts窗口下方的Close按钮退出到Tcl Scripts窗口,回到工程主界面。

此时,点击主界面的:Assignments→Pin Planner进入引脚分配界面。

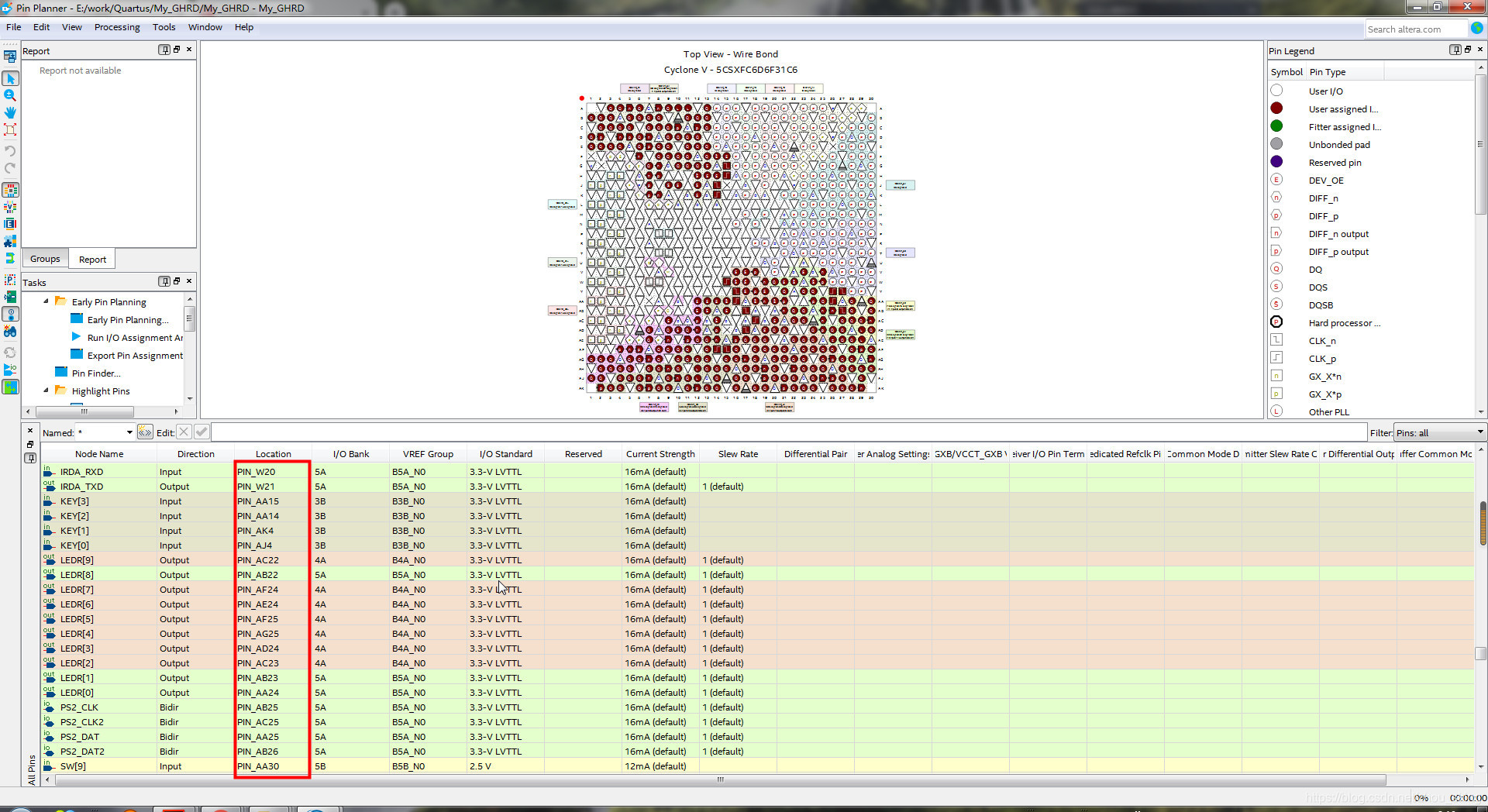

在引脚分配界面中,可以看到,引脚大部分已经被分配完成,未分配的引脚暂时不用担心它们,我们还没有用到。

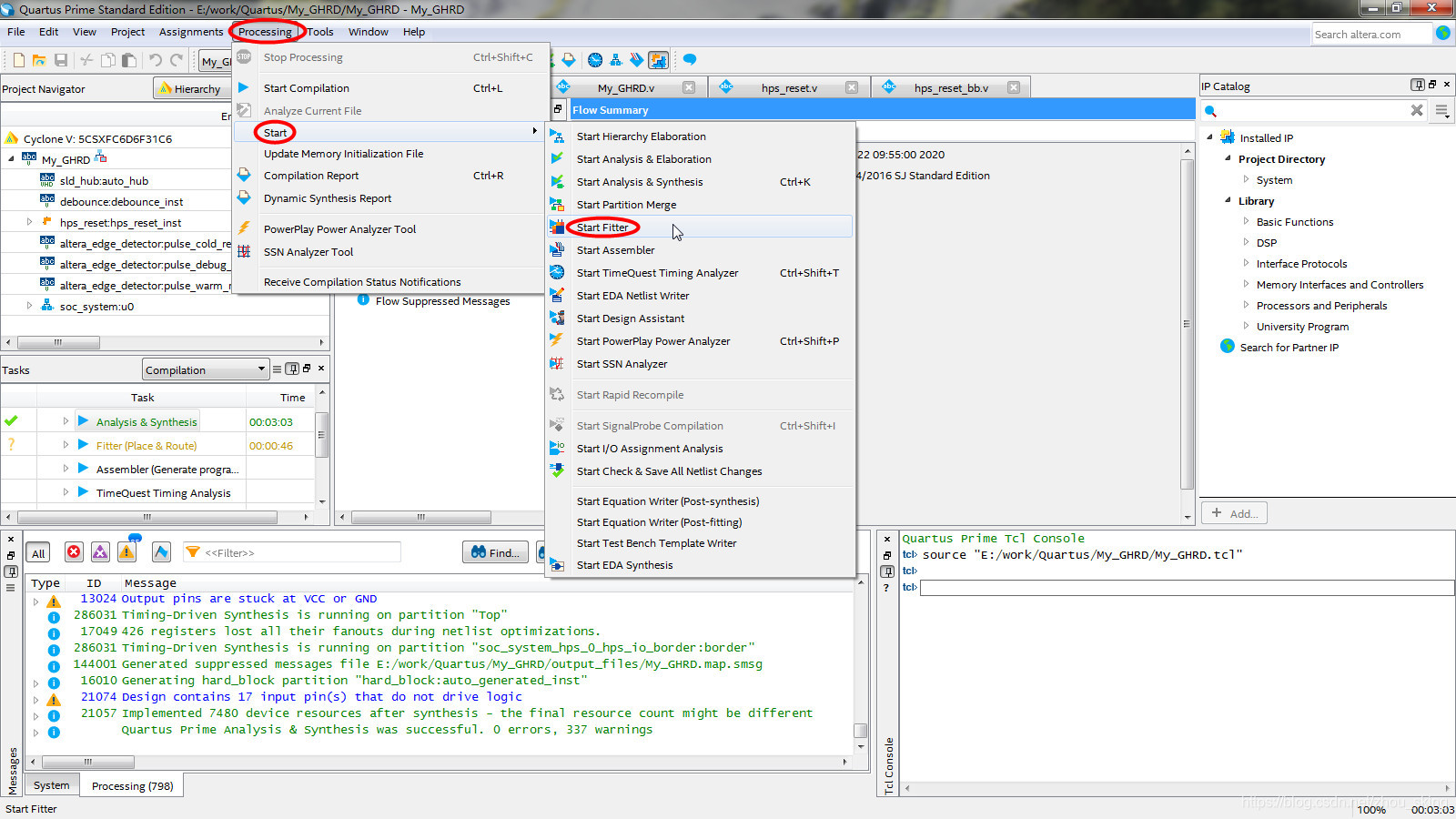

现在,我们开始对工程进行布局布线。点击:Processing→Start→Start Fitter。

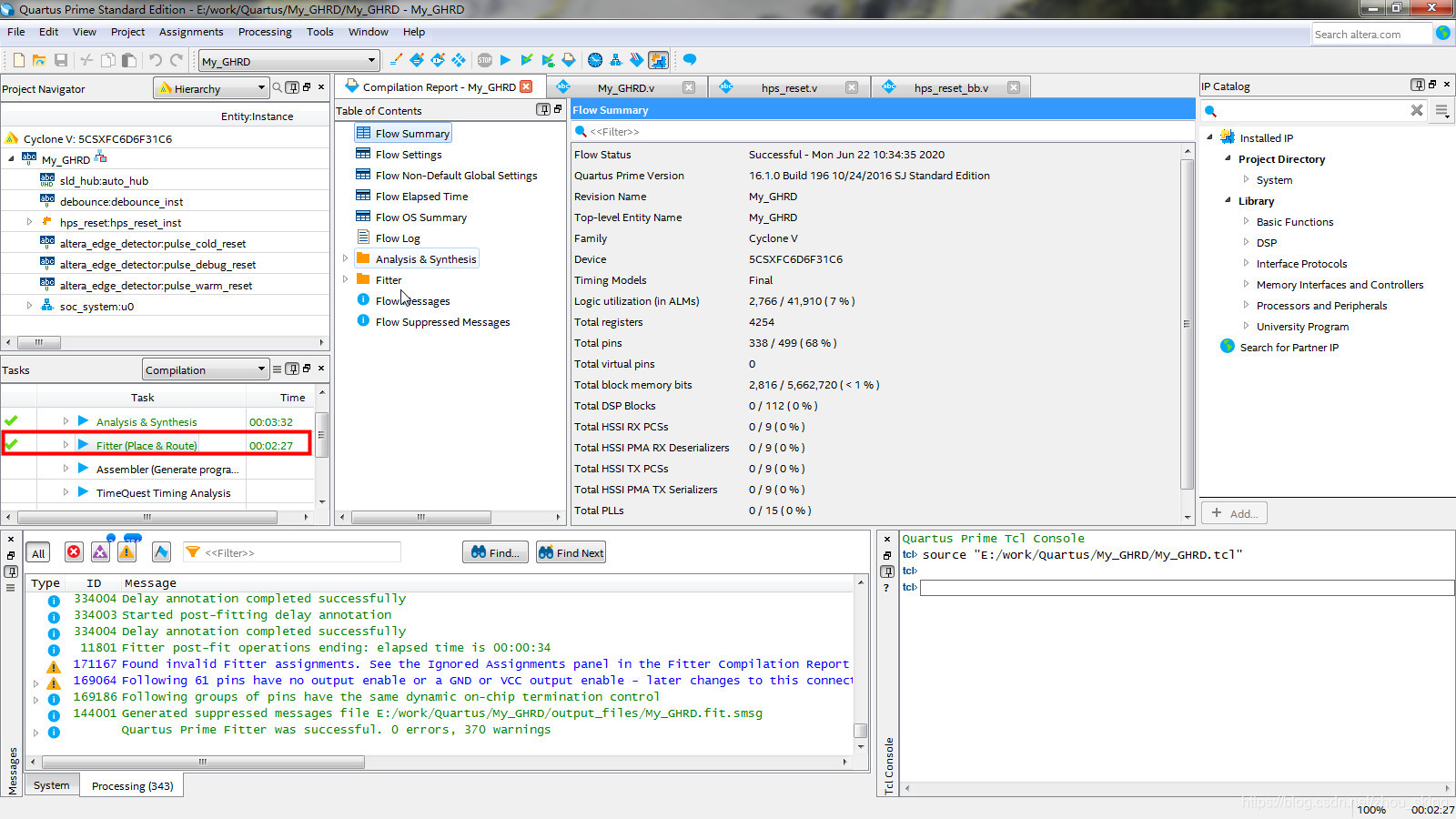

工程的布局布线通过后,主界面中左侧的Tasks窗口下的Fitter(Place & Route)栏前面会展示一个绿色的“√”,后面会显示布局布线所用的时间。

到此,基本上我们可以判断在逻辑上我们的设计已经没有问题了,接下来我们是可以进行工程的全编译了。但是,在实际的应用设计中我们还要考虑对信号的时序进行约束,尤其是具有 SDRAM DDR3这种高速存取器件的设计中。对于时序约束,我们可以利用DE10_Standard_GHRD工程中的时序约束文件:DE10_Standard_GHRD.sdc。同样的,将其复制到My_GHRD工程目录下,改名为:My_GHRD.sdc。

将时序约束文件添加进入工程,右击Project Navigator窗口下的工程名:My_GHRD,点击:Setting…按钮。

接下来会弹出Category界面,点击右侧的…按钮。

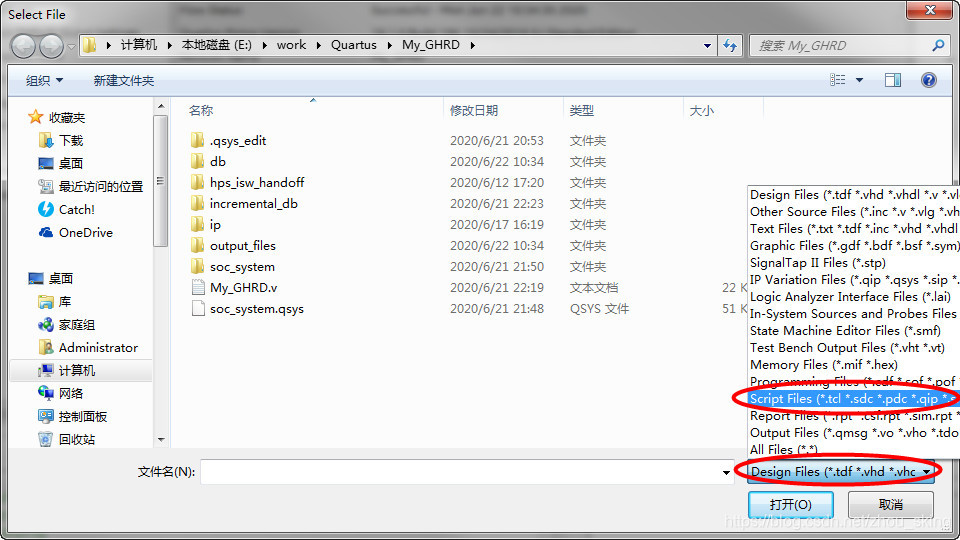

此时会弹出Select File界面,进入工程主目录下,点击右下角的文件类型选择按钮,选中:Script Files( * .tcl*.sdc*.pdc*.qip)一项。

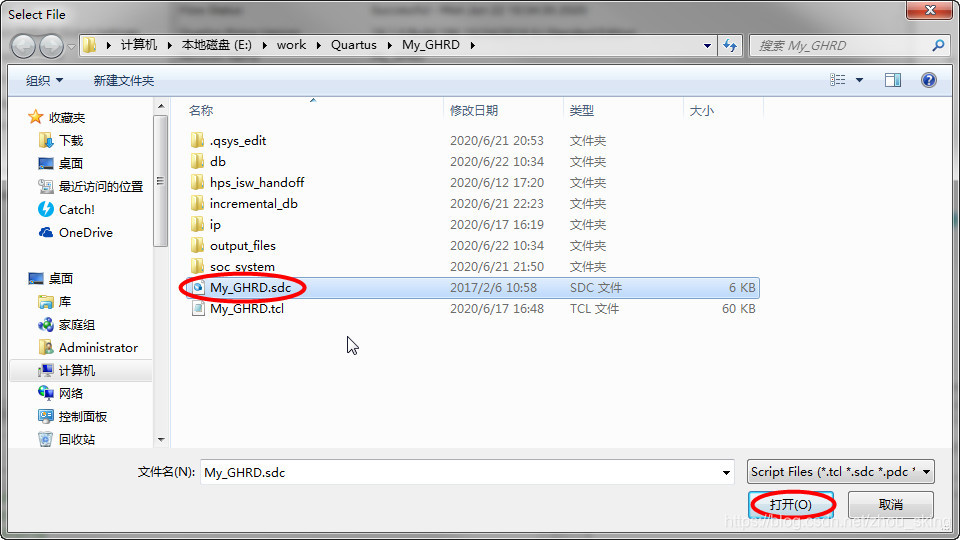

下找到时序约束文件My_GHRD.sdc并选中,然后点击右下角的“打开”按钮。

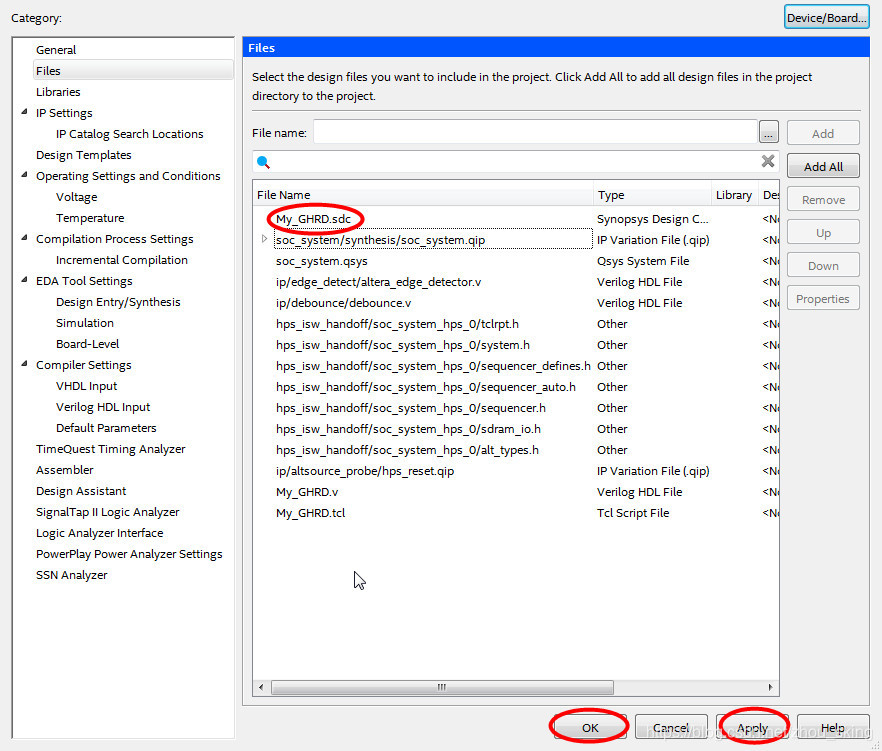

最后,可以在返回的Catagory界面中可以看到时序约束文件:My_GHRD.sdc文件已经被成功添加到工程中。依次点击右下角的Apply按钮和OK按钮退出该界面。

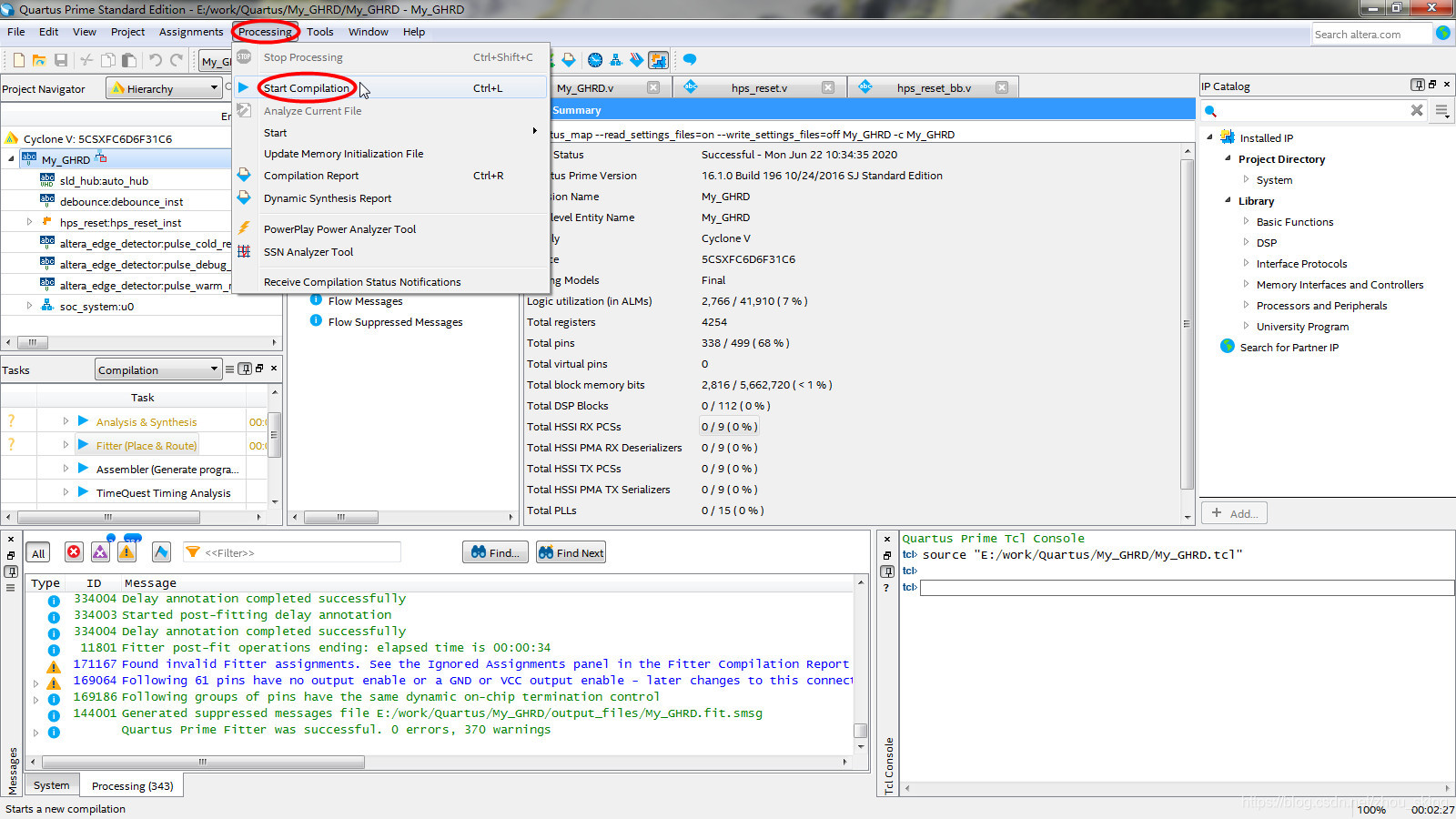

此时已经回到工程主界面,我们可以进行工程的全编译了。点击Processing→Start Compilation。

C语言设计

本节将介绍如何设计一个ARM C程序来控制PIO控制器led_pio。SoC EDS用于编译C项目。为了让ARM程序控制PIO组件led_pio,我们需要led_pio地址。使用Linux内置驱动程序’ /dev/mem '和mmap system-call可以将led_pio组件的物理基址映射到Linux应用软件可以直接访问的虚拟地址。

HPS头文件

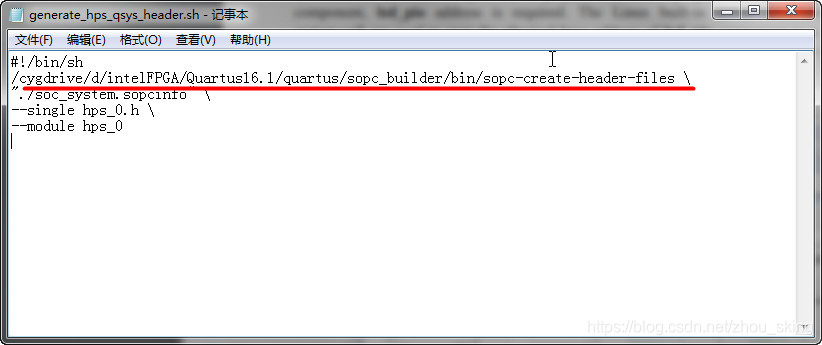

ARM C程序需要led_pio的组件信息,因为程序会尝试控制组件。这部分将会描述如何使用一个给定的Linux shell批处理文件将Qsys HPS信息提取到一个头文件中,这个头文件稍后将包含在C程序中。

上面提到的批处理文件名为:generate_hps_qsys_header.sh。它与DE10_Standard_GHRD工程位于同一个文件夹中。现在,我们要为工程My_GHRD生成头文件。首先,从DE10_Standard_GHRD工程目录下复制文件:generate_hps_qsys_header.sh到My_GHRD工程目录下。

接下来,使用记事本打开批处理文件:generate_hps_qsys_header.sh,确认文件中红线标注的路径下有应用程序:sopc-create-header-files.exe。其中,路径:/cygdrive/d/…表示D盘…。如果该路径下没有上述应用程序,读者需自行更改其中的路径。

注意,如果后面在SoC EDS命令shell中运行generate_hps_qsys_header.sh时,提示出现错误。(其实这个错误当时解决后忘记进行记录,好像是提示执行文件sopc-create-header-files的过程中sopcinfo2swinfo还是swinfo2header找不到之类的。)我们需要在文件sopc-create-header-files中锁定错误出现的行。对无法找到的应用程序路径进行指定。最终文件sopc-create-header-files中对应部分应该为:

cmd="sopcinfo2swinfo --input=$sopc_design_file --output=$swinfo_tmp_fname ${sopcinfo2swinfo_args[@]}"

/cygdrive/d/intelFPGA/Quartus16.1/quartus/sopc_builder/bin/sopcinfo2swinfo --input="$sopc_design_file" --output="$swinfo_tmp_fname" ${sopcinfo2swinfo_args[@]} || {echo "$PN: $cmd failed"exit 1

}cmd="swinfo2header --swinfo $swinfo_tmp_fname --sopc $sopc_design_file ${swinfo2header_args[@]}"

/cygdrive/d/intelFPGA/Quartus16.1/quartus/sopc_builder/bin/swinfo2header --swinfo "$swinfo_tmp_fname" --sopc "$sopc_design_file" "${swinfo2header_args[@]}" || {echo "$PN: $cmd failed"exit 1

}

一定注意,我们之间的Quartus安装路径是不同的,你需要根据自己的安装路径指定应用程序的路径,以便软件能够找到它们。

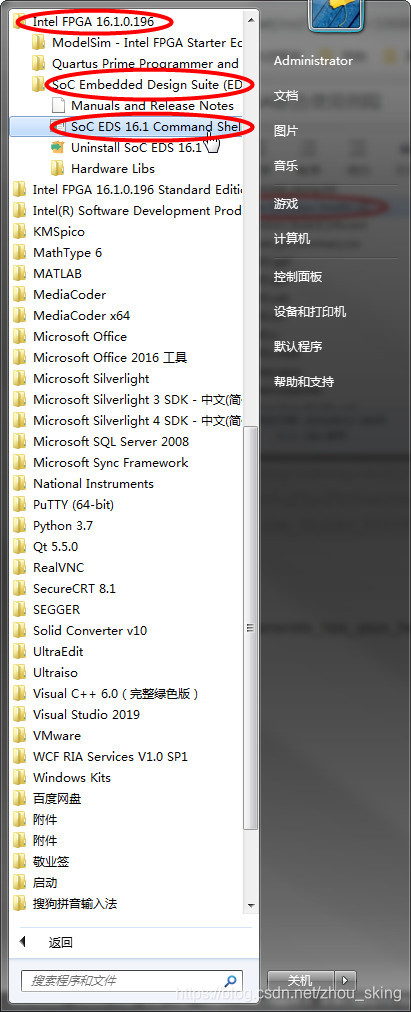

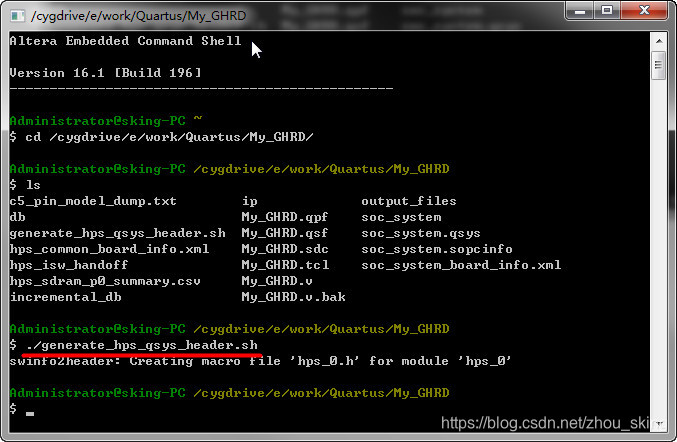

然后,启动SoC EDS命令shell

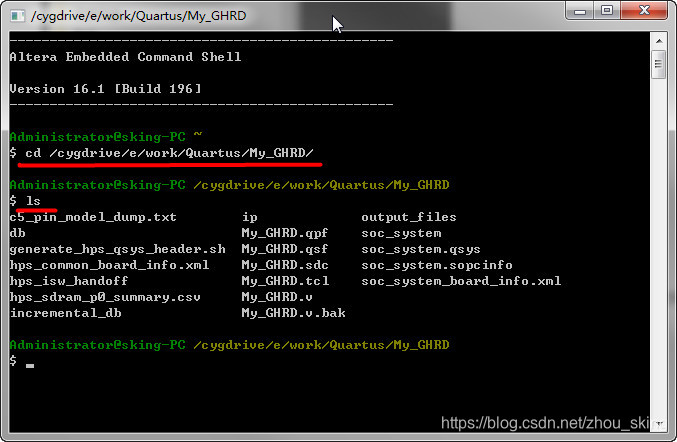

在SoC EDS Command Shell中,转到My_GHRD工程目录下。其中我的工程目录为:E:\work\Quartus\My_GHRD。读者根据自己的工程目录路径设置,为了输入方便,可以使用Tab键自动补全功能。注意:在E盘,路径就是:/cygdrive/e/…。

执行批处理文件:generate_hps_qsys_header.sh by

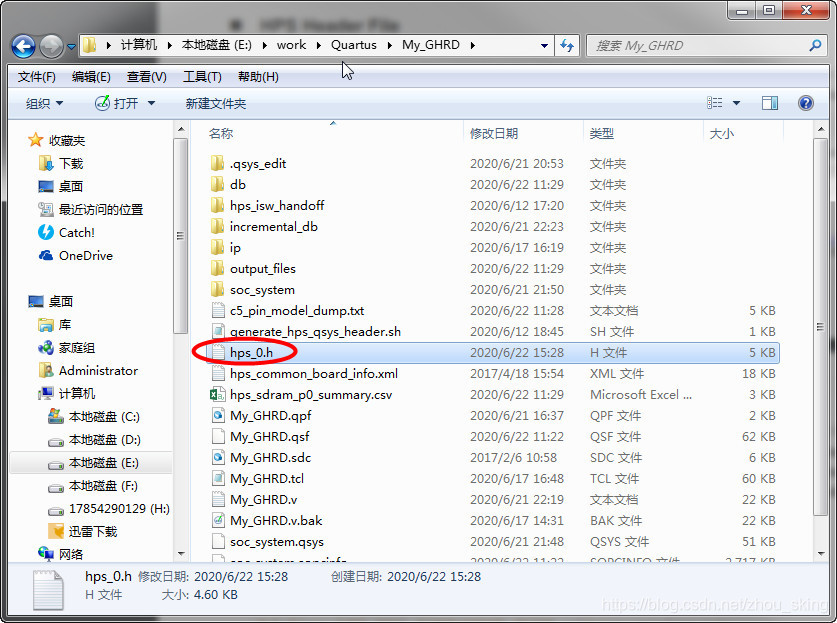

此时,会在My_GHRD工程目录下生成HPS头文件:hps_0.h。

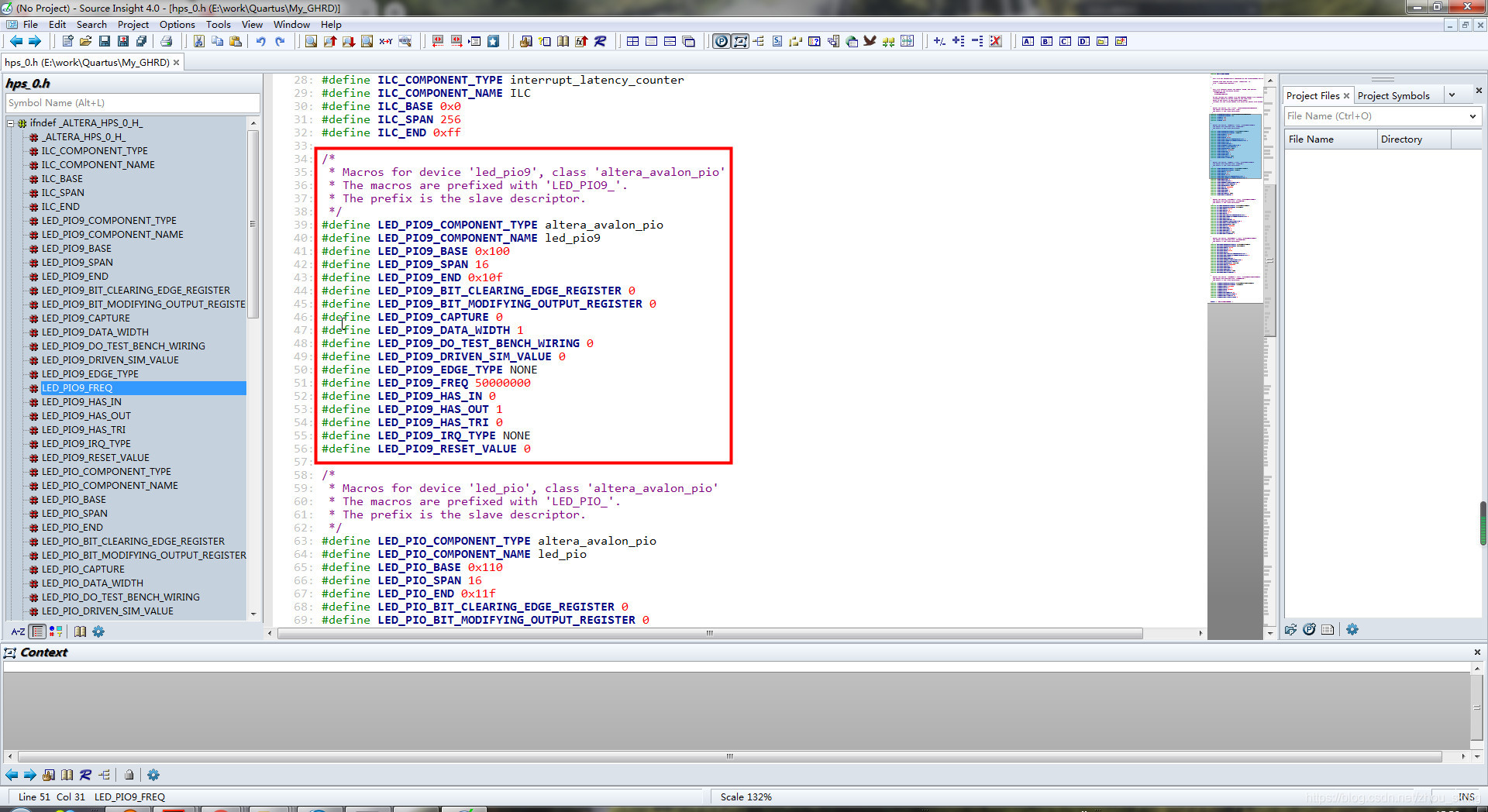

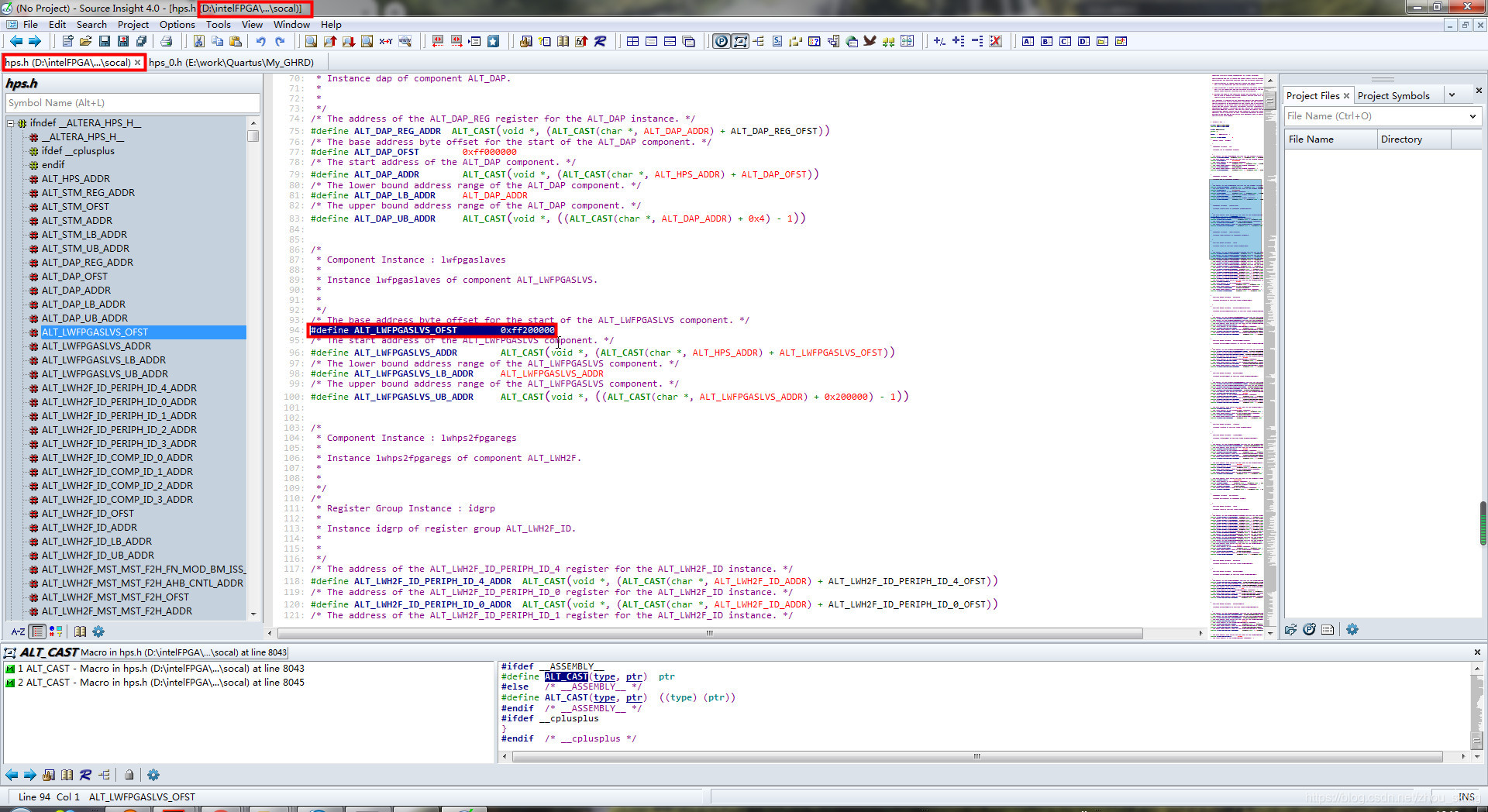

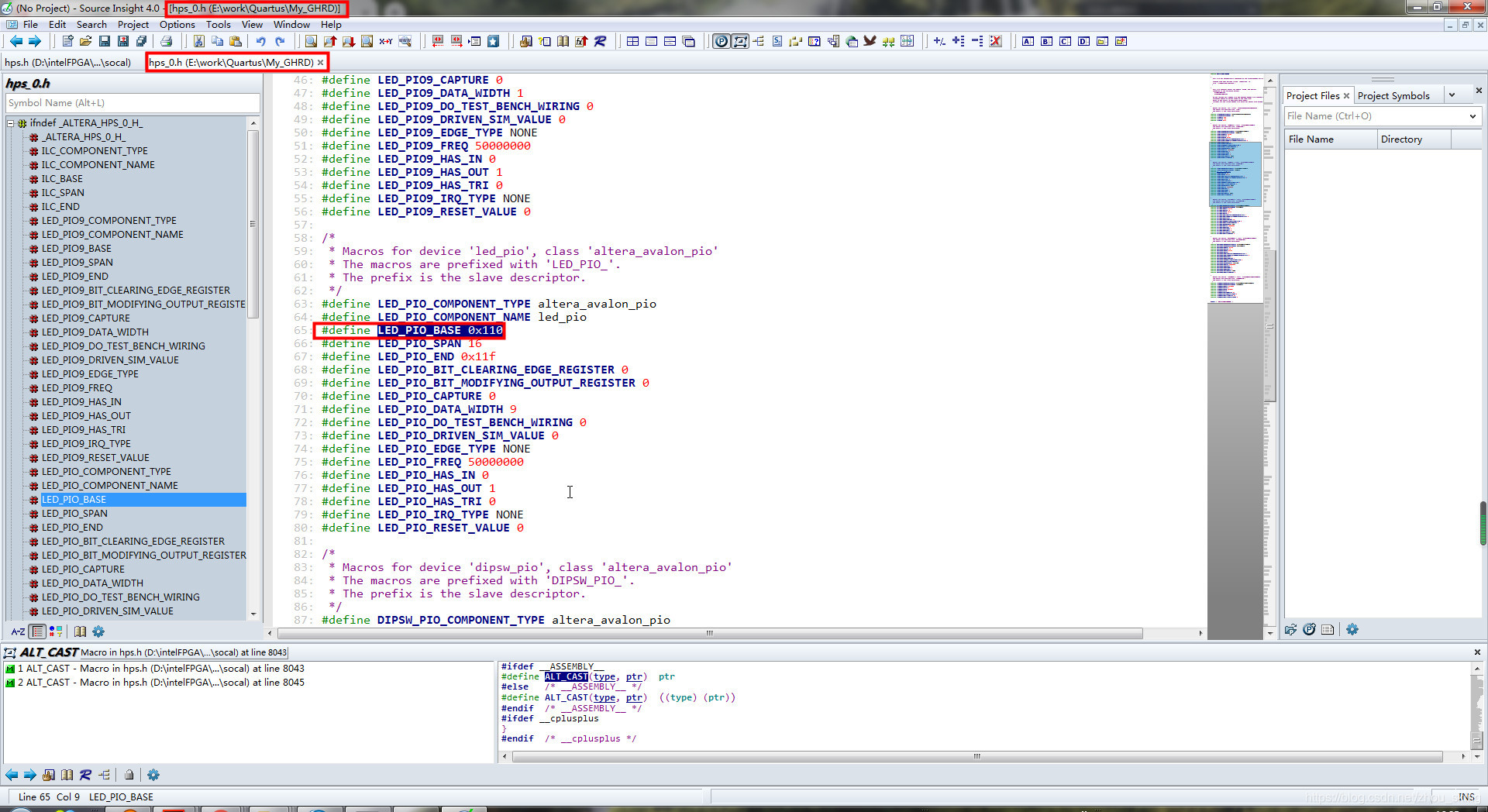

现在,我们已经得到所需的头文件:hps_0.h。我们可以用一些代码查看编辑软件查看一下它里面的内容,我这里用的代码查看编辑软件是Source Insight。可以看到,生成的头文件:hps_0.h中已经为我们新增的PIO模块led_pio9生成了一系列宏定义。在头文件中,led_pio9的基地址由一个常量LED_PIO9_BASE表示,led_pio9的数据宽度由一个常量LED_PIO9_DATA_WIDTH表示,这两个常量将会在后面的C语言代码中被使用。

LED_PIO地址映射

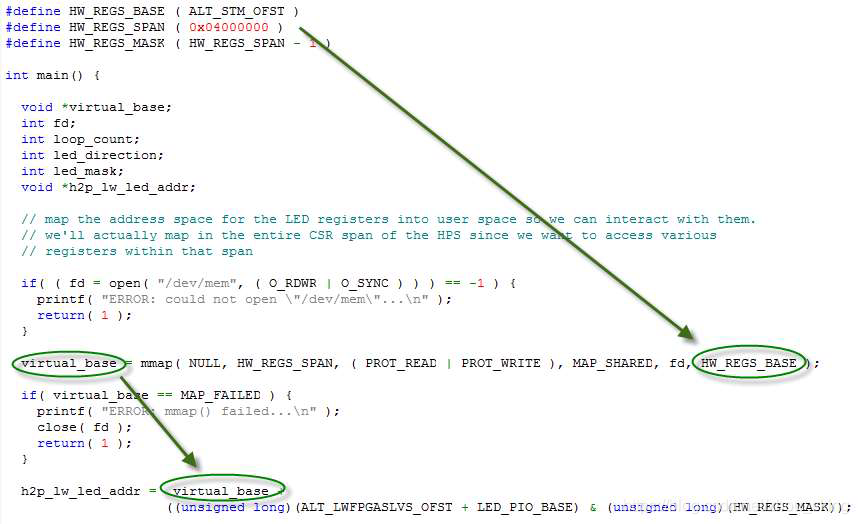

本部分将描述如何将pio_led的物理地址映射为应用程序软件可以访问的虚拟地址。下图显示了C程序派生led_pio基址的虚拟地址。

首先,open 通过系统调用打开内存设备驱动程序" /dev/mem ",然后mmap通过系统调用用于将HPS物理地址映射为由void指针变量virtual_base表示的虚拟地址。代码将外围区域的物理基地址(HW_REGS_BASE = 0xfc000000)映射为一个基于虚拟地址的virtual_base。对于任何外围区域的控制器,用户可以通过其相对于外围区域的偏移量与基于的虚拟地址virtual_base进行叠加来计算任何外围区域的控制器的虚拟地址。根据这个规则,可以通过将下面两个偏移地址添加到virtual_base来计算led_pio的虚拟地址:

- 轻量级的HPS-to- fpga AXI总线相对于HPS基址的偏移地址

- Pio_led 相对 于 Lightweight HPS-to-FPGA AXI 总线的偏移地址

第一个偏移地址是0xff200000,在头文件hps.h中定义为常量ALT_LWFPGASLVS_OFST。头文件hps.h是SoC EDS中的头文件。位于Quartus安装文件夹:D:\intelFPGA\SoCEDS16.1\embedded\ip\altera\hps\altera_hps\hwlib\include\soc_cv_av\socal中。

第二个偏移地址是0x110,在头文件hps_0.h中定义为:LED_PIO_BASE

LED_PIO的虚拟地址由一个void指针变量h2p_lw_led_addr表示。应用程序可以直接使用指针变量来访问控制器中的寄存器LED_PIO。

控制LED

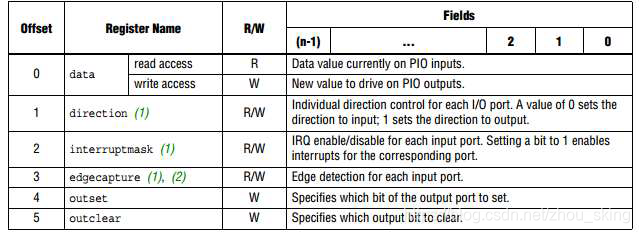

C程序员需要理解LED_PIO的PIO核的寄存器映射,然后才能控制它。下图显示了PIO核的寄存器映射。每个寄存器的宽度是32位。详情可以参阅PIO Core数据手册。对于led控制,我们只需要将输出值写入相对于基于地址0x10040的偏移地址为0寄存器。因为DE10-Standard板上的LED是高电平触发的,将值0x00000000写入偏移地址为0的寄存器将关闭所有9个红色led。DE10-Standard上有10个红色led,其中9个连接到这个控制器上。最后一个LED (LED0)用于模拟FPGA心跳。将值0x000001ff写入偏移地址为0寄存器将打开所有9个红色led。在C程序中,向pio_led的0偏移寄存器写入值0x000001ff可以表示为:

*(uint32_t *)h2p_lw_led_addr = 0x000001ff;

这条语句会将void指针赋值给uint32_t指针,所以C编译器知道写一个32位的值0x000001ff到虚拟地址h2p_lw_led_addr里面。

主程序

在友晶科技提供的例程中,又一个应用程序例程HPS_FPGA_LED。它的功能为:控制LEDR1-9进行LED移位闪烁操作,完成60次循环移位闪烁后,程序终止。我们的设计目标是:控制LEDR1-8进行LED移位闪烁操作,LEDR9随着LEDR1-8每一次移位而闪烁一次,完成60次循环移位闪烁后,程序终止。例程HPS_FPGA_LED的功能与我们的设计目标非常接近,所以我们可以在例程HPS_FPGA_LED的设计基础上进行更改。

首先,在光盘目录下找到例程HPS_FPGA_LED所在的文件夹:DE10-Standard_v.1.2.8_SystemCD\Demonstration\SoC_FPGA\HPS_FPGA_LED。将应用程序目录HPS_FPGA_LED复制到My_GHRD工程目录下,并把My_GHRD工程目录下的hps_0.h放到应用程序目录HPS_FPGA_LED下。

现在就可以开始根据我们的目标修改应用程序目录HPS_FPGA_LED下的:main.c。

我们要在主程序中设置一个void指针变量h2p_lw_led9_addr来存放新增的PIO组件LED_PIO9的虚拟地址。

h2p_lw_led9_addr=virtual_base + ( ( unsigned long )( ALT_LWFPGASLVS_OFST + LED_PIO9_BASE ) & ( unsigned long)( HW_REGS_MASK ) );

对于LEDR9的控制,我们只需要在虚拟地址h2p_lw_led9_addr所指向的地址空间中写入0x1点亮LEDR9、写入0x0熄灭LEDR9。

*(uint32_t *)h2p_lw_led9_addr = 0x1; //点亮LEDR9

*(uint32_t *)h2p_lw_led9_addr = 0x0; //熄灭LEDR9

但是为了使LEDR9随着LEDR1-8的移位进行闪烁,我们可以设置一个int变量n,让其随着LEDR1-8移位进行+1操作。我们对变量n进行取余操作后,将余值写入虚拟地址h2p_lw_led9_addr所指向的地址空间中即可。

*(uint32_t *)h2p_lw_led9_addr = n%2;

n = n+1;

最终,main.c文件内容如下:

/*

This program demonstrate how to use hps communicate with FPGA through light AXI Bridge.

uses should program the FPGA by GHRD project before executing the program

refer to user manual chapter 7 for details about the demo

*/#include <stdio.h>

#include <unistd.h>

#include <fcntl.h>

#include <sys/mman.h>

#include "hwlib.h"

#include "socal/socal.h"

#include "socal/hps.h"

#include "socal/alt_gpio.h"

#include "hps_0.h"#define HW_REGS_BASE ( ALT_STM_OFST )

#define HW_REGS_SPAN ( 0x04000000 )

#define HW_REGS_MASK ( HW_REGS_SPAN - 1 )int main() {void *virtual_base;int n=0;int fd;int loop_count;int led_direction;int led_mask;void *h2p_lw_led_addr;void *h2p_lw_led9_addr;// map the address space for the LED registers into user space so we can interact with them.// we'll actually map in the entire CSR span of the HPS since we want to access various registers within that spanif( ( fd = open( "/dev/mem", ( O_RDWR | O_SYNC ) ) ) == -1 ) {printf( "ERROR: could not open \"/dev/mem\"...\n" );return( 1 );}virtual_base = mmap( NULL, HW_REGS_SPAN, ( PROT_READ | PROT_WRITE ), MAP_SHARED, fd, HW_REGS_BASE );if( virtual_base == MAP_FAILED ) {printf( "ERROR: mmap() failed...\n" );close( fd );return( 1 );}h2p_lw_led_addr=virtual_base + ( ( unsigned long )( ALT_LWFPGASLVS_OFST + LED_PIO_BASE ) & ( unsigned long)( HW_REGS_MASK ) );h2p_lw_led9_addr=virtual_base + ( ( unsigned long )( ALT_LWFPGASLVS_OFST + LED_PIO9_BASE ) & ( unsigned long)( HW_REGS_MASK ) );// toggle the LEDs a bitloop_count = 0;led_mask = 0x01;led_direction = 0; // 0: left to right directionwhile( loop_count < 60 ) {// control led*(uint32_t *)h2p_lw_led_addr = ~led_mask;*(uint32_t *)h2p_lw_led9_addr = n%2;n=n+1;// wait 100msusleep( 100*1000 );// update led maskif (led_direction == 0){led_mask <<= 1;if (led_mask == (0x01 << (LED_PIO_DATA_WIDTH-1)))led_direction = 1;}else{led_mask >>= 1;if (led_mask == 0x01){ led_direction = 0;loop_count++;}}} // while// clean up our memory mapping and exitif( munmap( virtual_base, HW_REGS_SPAN ) != 0 ) {printf( "ERROR: munmap() failed...\n" );close( fd );return( 1 );}close( fd );return( 0 );

}Makefile与编译

Makefile的内容如下:该程序包括SoC EDS提供的头文件。在Makefile中,还指定了ARM-linux交叉编译。

#

TARGET = HPS_FPGA_LED#

ALT_DEVICE_FAMILY ?= soc_cv_av

SOCEDS_ROOT ?= $(SOCEDS_DEST_ROOT)

HWLIBS_ROOT = $(SOCEDS_ROOT)/ip/altera/hps/altera_hps/hwlib

CROSS_COMPILE = arm-linux-gnueabihf-

CFLAGS = -g -Wall -D$(ALT_DEVICE_FAMILY) -I$(HWLIBS_ROOT)/include/$(ALT_DEVICE_FAMILY) -I$(HWLIBS_ROOT)/include/

LDFLAGS = -g -Wall

CC = $(CROSS_COMPILE)gcc

ARCH= armbuild: $(TARGET)

$(TARGET): main.o $(CC) $(LDFLAGS) $^ -o $@

%.o : %.c$(CC) $(CFLAGS) -c $< -o $@.PHONY: clean

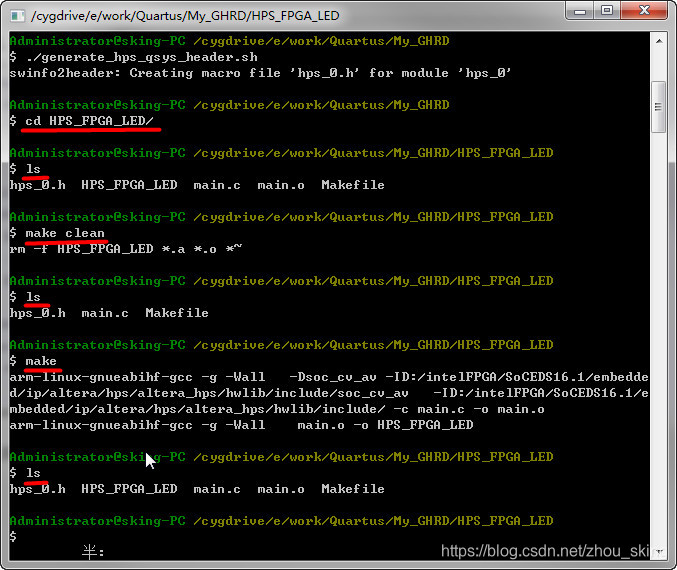

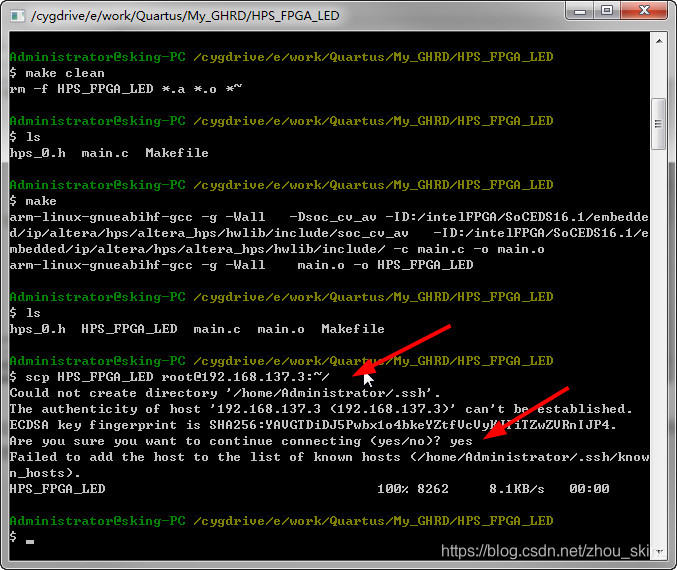

clean:rm -f $(TARGET) *.a *.o *~ 要编译这个应用程序HPS_FPGA_LED,在SoC EDS Command Shell中进入应用程序目录HPS_FPGA_LED下。

cd HPS_FPGA_LED/

使用ls命令查看HPS_FPGA_LED目录下的文件,可以发现其中含有根据原来的main.c文件编译出的main.o文件和可执行文件:HPS_FPGA_LED。

ls

我们需要清除根据原来的main.c文件编译出的main.o文件和可执行文件:HPS_FPGA_LED。现在执行make clean命令。

make clean

再次使用ls命令,可以看到根据原来的main.c文件编译出的main.o文件和可执行文件:HPS_FPGA_LED已经被清除了。

ls

现在,使用make命令根据更改后的main.c文件编译出main.o文件和可执行文件:HPS_FPGA_LED。

make

整个操作过程如下图所示:

至此,我们已经完成了硬件设计和应用程序设计两方面的设计工作。接下来就可以分别将包含有硬件逻辑信息的文件My_GHRD.sof和可执行文件HPS_FPGA_LED下载到DE10_Standard开发板上执行了。

系统测试

现在,我们需要在DE10_Standard开发板上进行系统测试,验证我们之前硬件逻辑设计和应用程序设计。这部分主要包括硬件逻辑的下载和应用程序的运行,硬件逻辑信息包含在文件My_GHRD.sof中,我们需要用它对FPGA进行编程;应用程序的运行其实就是在开发板上执行可执行文件HPS_FPGA_LED。

启动开发板

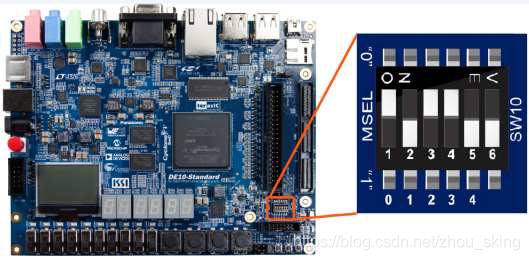

在进行硬件逻辑的下载和应用程序的运行之前,我们首先要对开发板进行各种线缆的连接和启动模式的配置。其中,线缆的连接主要包括:电源线、USB Blaster II线、串口线和网口线。配置模式的选择就是将开关SW10的MSEL[4:0]引脚配置为:01010,开关如下图所示,使得开发板可以从SD卡引导Linux系统启动。

连接好各种线缆后,打开DE10_Standard开发板上的串口。

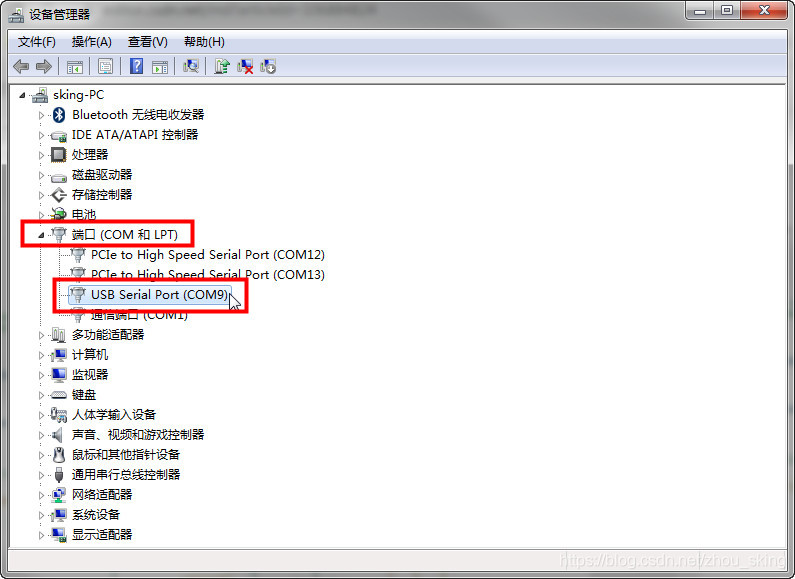

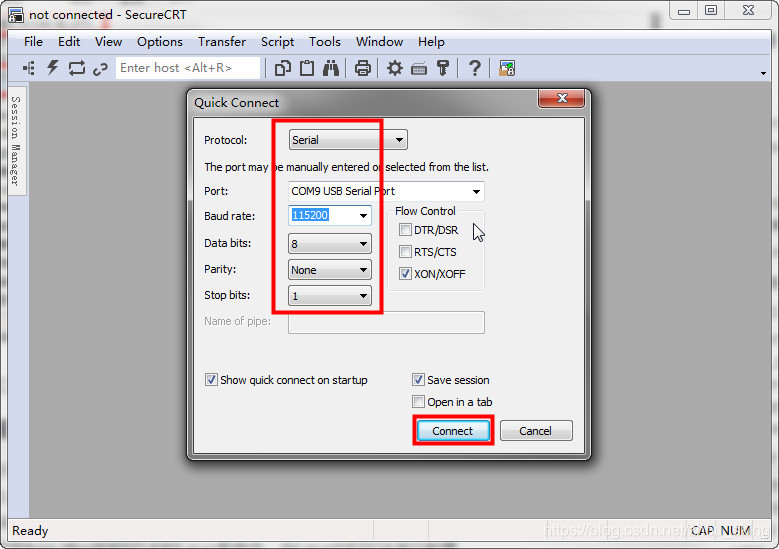

首先,确认开发板连接到电脑上的端口号。打开:控制面板→设备管理器→端口,可以看到:USB Serial Port(COM9),这个COM9就是电脑为我们的开发板串口分配的端口号。

打开串口工具SecureCRT

设置以下参数:

- Protocol:Serial

- Port:COM9 USB Serial Port

- Baud rate:115200

- Data bits:8

- Parity:None

- Stop bits:1

点击:Connect按钮。

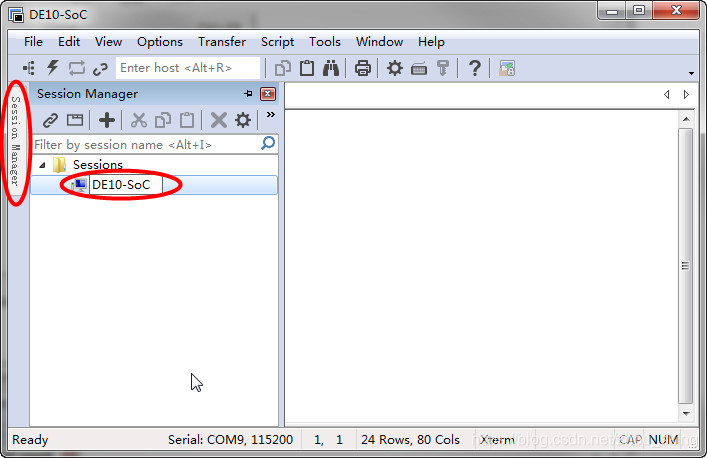

点击SecureCRT主界面左侧的:Session Manager。选中:serial-com9,右击选中:Rename。重命名为:DE10-SoC。

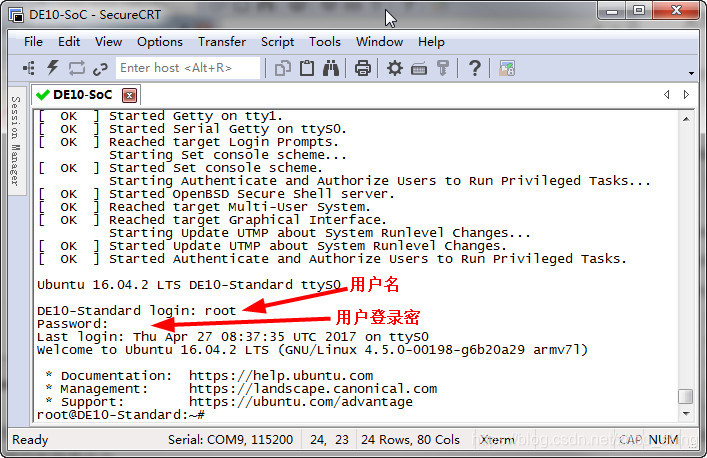

按下开发板的电源开关,启动开发板。此时会在串口工具SecureCRT中看到开发板启动信息。等待提示输入用户名登录命令。在用户登录处键入:root,回车。用户登录密码处不用填写,直接回车。

到此,开发板启动的相关工作已经完成。

硬件逻辑下载

硬件逻辑下载的方式有很多种。可以通过USB Blaster II缆线将包含有硬件逻辑信息的文件My_GHRD.sof下载到SoC FPGA的FPGA上;也可以通过USB Blaster II缆线将包含有硬件逻辑信息的文件My_GHRD.jic下载到EPCS中;还可以通过串口或者网口将有硬件逻辑信息的文件soc_sytem.rbf和设备树覆盖文件fpga.dtbo放到SD卡的Linux系统中,由Linux对FPGA进行配置。

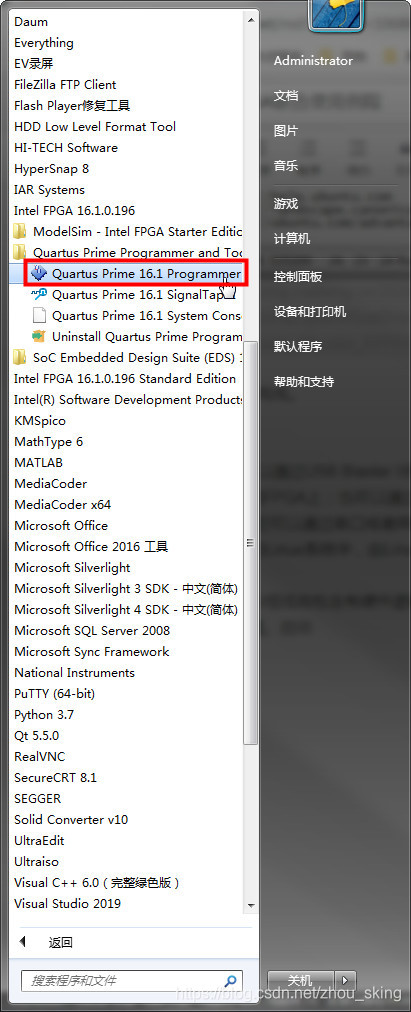

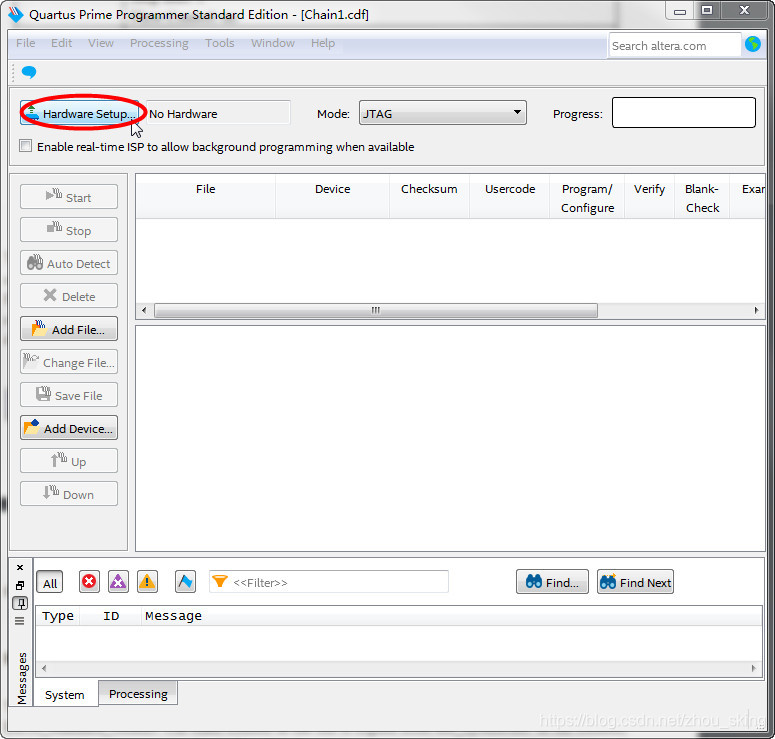

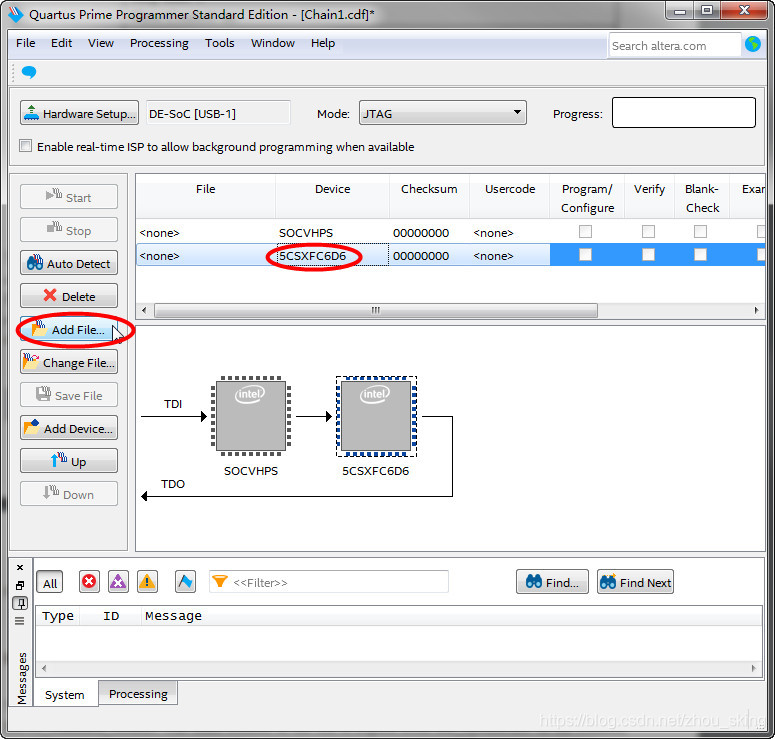

这里为了方便,我们采用通过JTAG缆线将包含有硬件逻辑信息的文件My_GHRD.sof下载到SoC FPGA的FPGA上的方式对FPGA进行配置。启动Quartus Prime Programmer。

进入Quartus Prime Programmer Standard Edition界面后,点击:Hardware Setup…按钮,检测下载用于My_GHRD.sof的JTAG链。

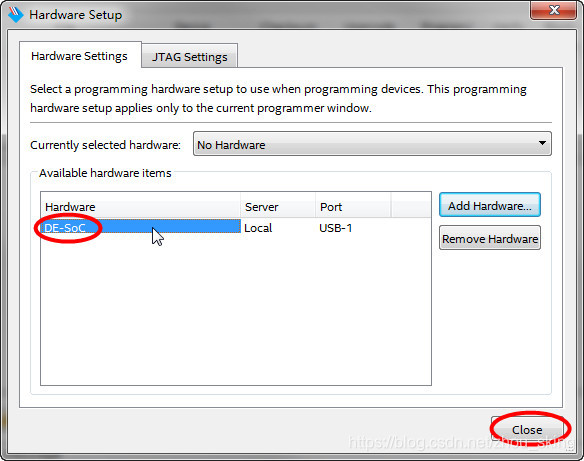

在Hardware Setup界面下,双击:DE-SoC,然后点击:Close按钮退出该界面。如果该界面下没有显示DE-SoC选项,在确保开发板上电,且JTAG线缆连接无误的情况下,关闭该界面重新进入几次即可。

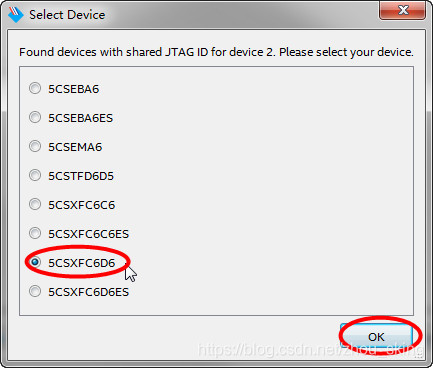

退回Quartus Prime Programmer Standard Edition界面后,点击:Auto Detect按钮,自动检测JTAG链上的器件。

此时会弹出Select Device界面,提示我们选择我们所用的SoC FPGA型号,选择:5CXFC6D6。然后点击右下角OK按钮退出该界面。

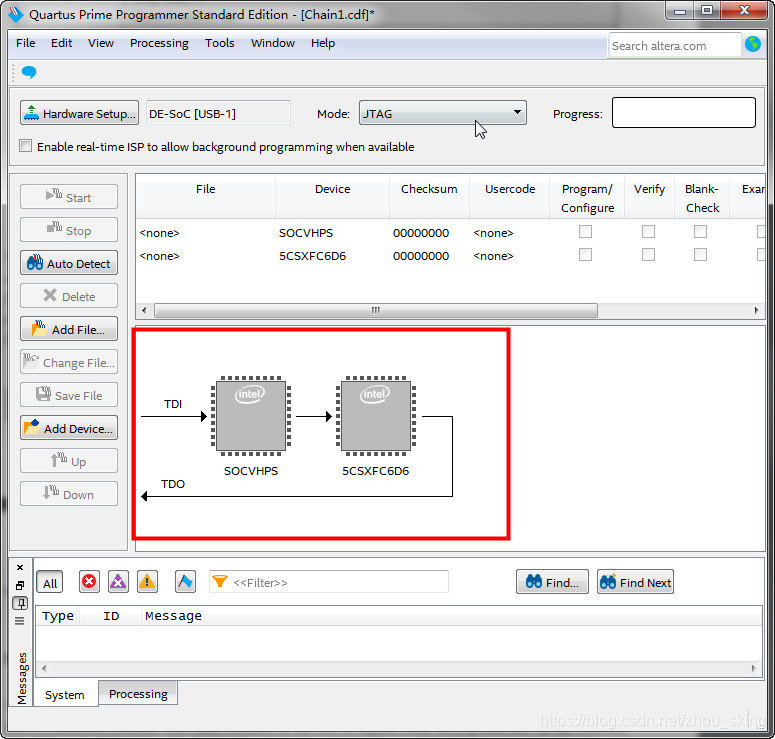

此时,Quartus Prime Programmer Standard Edition界面将会显示我们JTAG链上的器件。

选中:5CXFC6D6,然后点击左侧的:Change File…按钮,为5CXFC6D6添加配置文件。

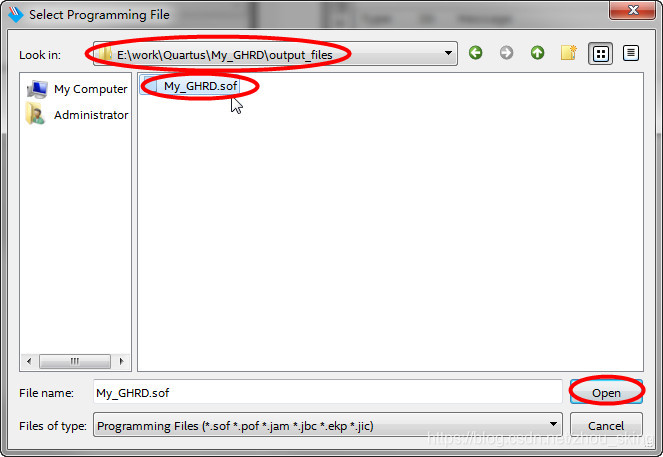

在弹出的Select Programming File界面下,找到My_GHRD工程目录下的:output_files/My_GHRD.sof并选中,然后点击:Open。

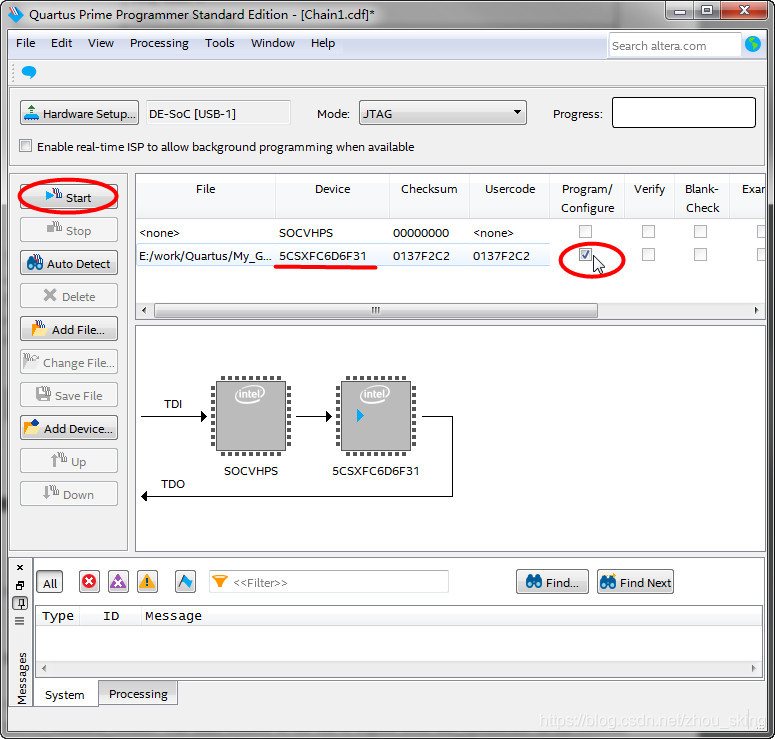

返回Quartus Prime Programmer Standard Edition界面后,找到5CSXFC6D6F31所在行,勾选:Program/Configure。然后,点击Start按钮开始配置FPGA。

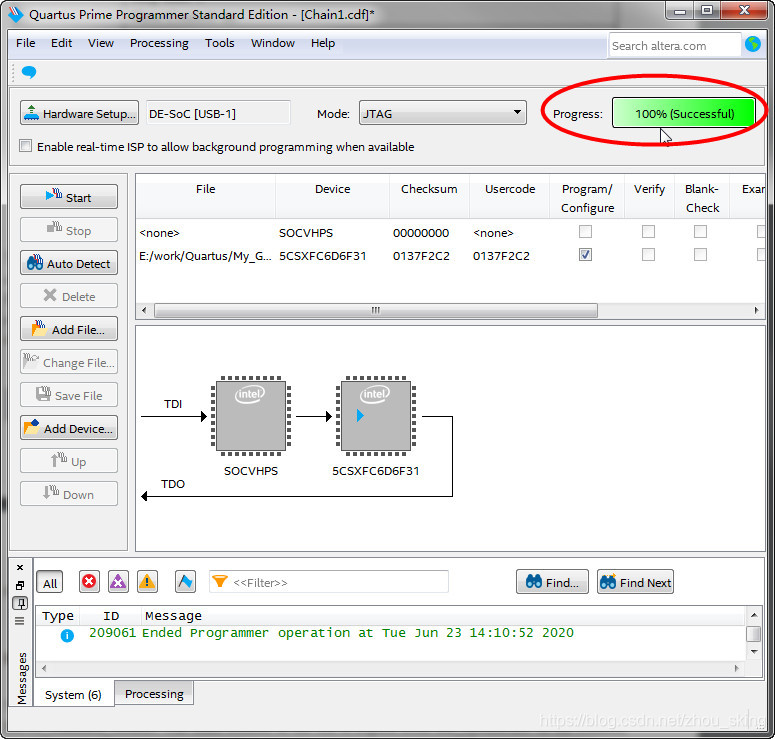

最后,在Process栏可以看到配置进度。此处显示:100%(Successful)表明FPGA配置成功。

应用程序运行

在完成FPGA的硬件逻辑配置后,我们就可以将应用程序发送到开发板中执行了。

文件传输

我们采用网口文件传输方式将应用程序可执行文件HPS_FPGA_LED发送开发板的Linux系统中。

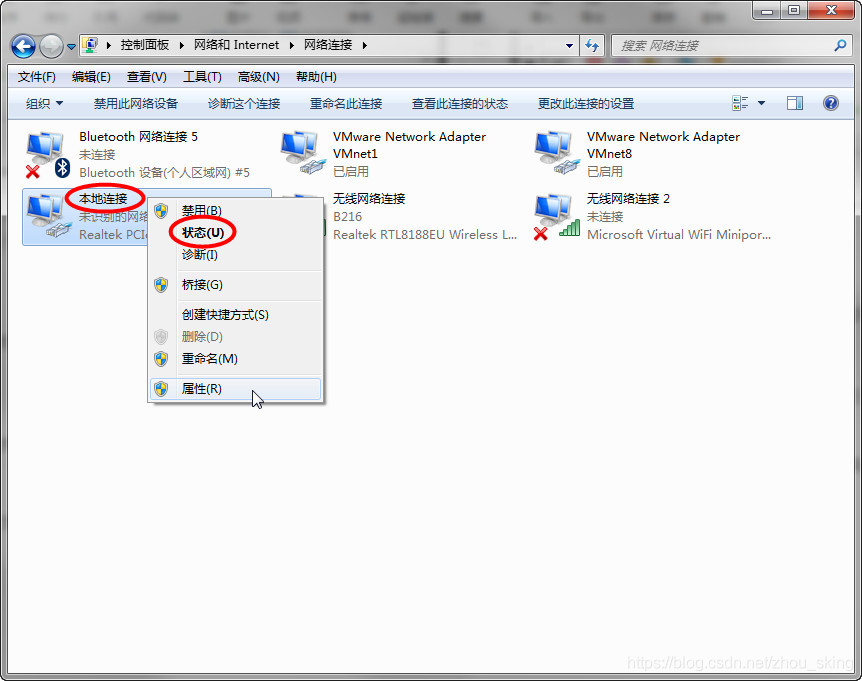

在使用网口传输文件时,我们需要设置开发板和电脑在同一个网段下。首先,我们要确认电脑的IP地址。打开:控制面板→网络与共享中心,点击左侧:更改适配器设置。

接下来,我们需要查看电脑网络的状态信息,因为我们的电脑和开发板是通过网线进行连接的,我们应该查看本地连接的状态信息。选中本地连接,右击选择:状态。

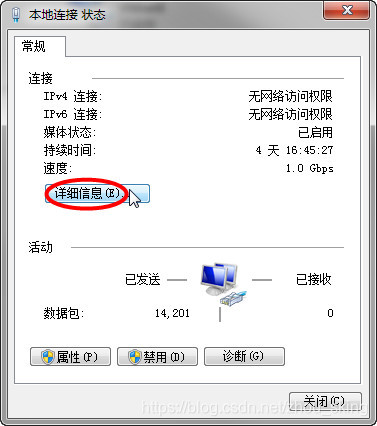

点击:详细信息。

在网络连接详细信息界面中,可以看到,本地连接的IP地址(IPv4地址)为:192.168.137.1。之后就可以退出查看IP地址所打开的一系列界面了。

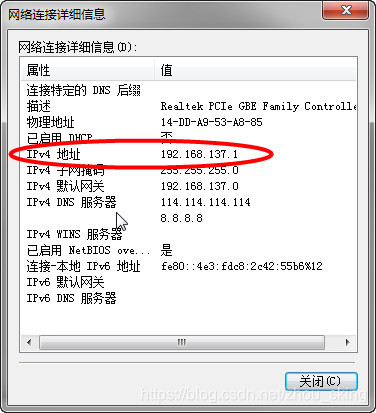

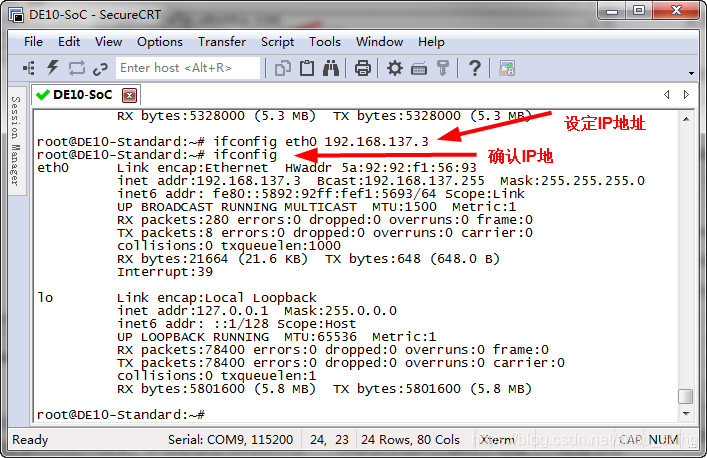

接下来,我们需要设置开发板的IP地址和电脑本地连接的IP地址在同一网段,即:192.168.137.*。我们暂且将其设定为:192.168.137.3。

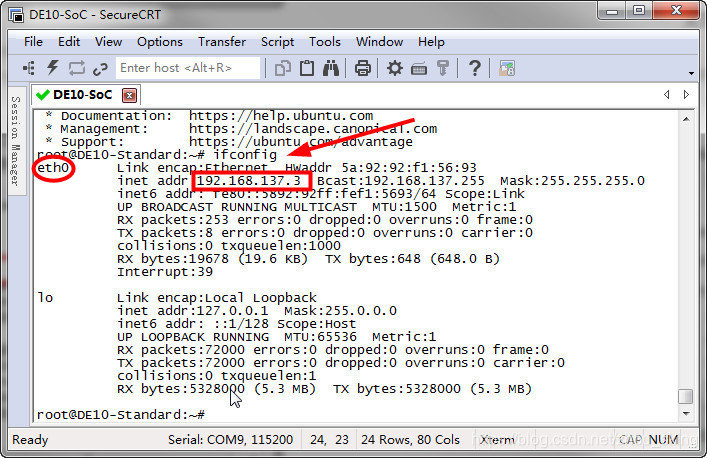

进入串口工具SecureCRT中,输入命令:ifconfig,查看当前开发板的网络端口号及其IP地址信息。可以看到,开发板的网络端口号为:eth0,IP地址为:192.168.137.3。这已经是我们要设定的IP地址了。

当然,如果我们是第一次在开发板上运行友晶科技提供的镜像,这时启动的Linux系统中的网络IP地址并非如此,我们需要对其进行设定。IP地址设定有两种方法:一种是设定临时的静态IP地址;一种是设定永久的静态IP地址。前者在关闭开发板后IP地址将自动失效;后者的IP地址是永久生效的,除非再次更改。

我们这里只设定临时静态IP地址。在串口工具中输入命令:ifconfig eht0 192.168.137.3,即可设定IP地址。可以再次运行命令:ifconfig确认IP地址设定是否成功。

IP地址设置完成后,我们就可以进行文件传输了。进入SoC EDS Command Shell中,进入应用程序所在的目录下。输入:scp HPS_FPGA_LED root@192.168.137.3:~/,回车。此时将会启动文件传输,接着在:Are you sure you want to continue connecting <yes/no>?后面输入:yes,可执行文件HPS_FPGA_LED将会自动传输到开发板上Linux系统的root用户主目录下。

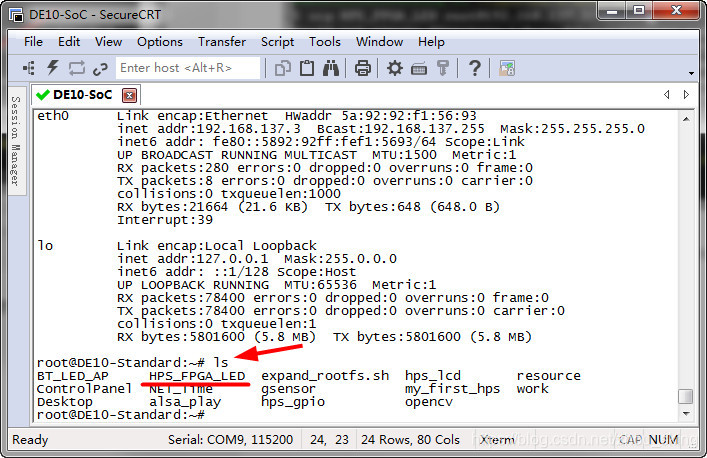

在串口工具SecureCRT中,输入命令ls可以查看当前所在的root用户主目录下已经存在可执行文件HPS_FPGA_LED。

至此,使用网口进行文件传输已经完成。

当然,我们也可以采用比较通用的FTP服务通过网口进行传输,读者可以自行学习。

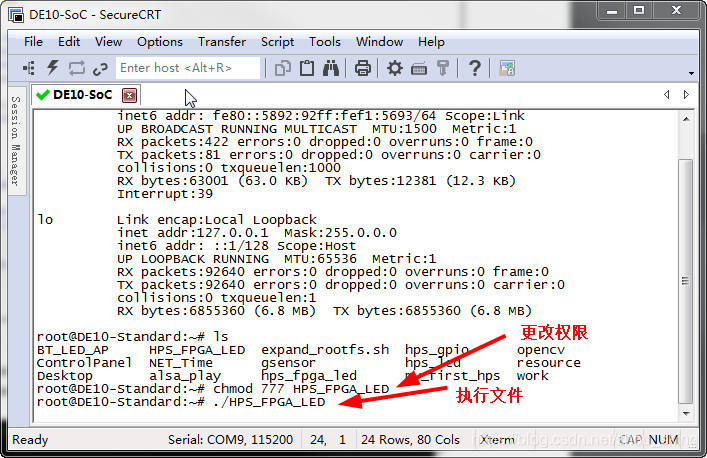

文件执行

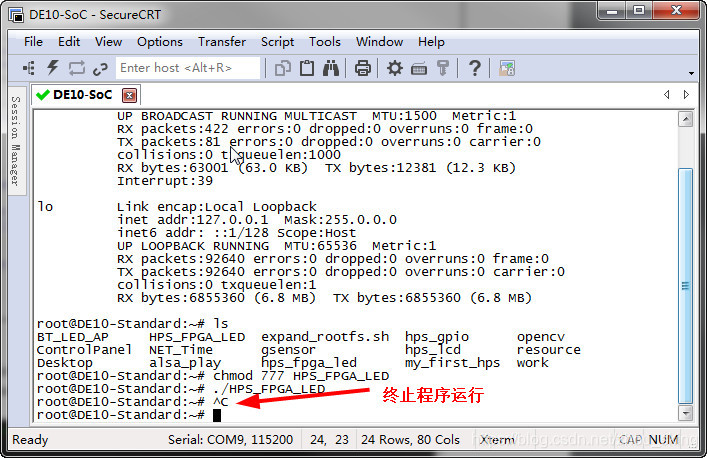

文件执行前我们需要更改可执行文件HPS_FPGA_LED的权限。在串口工具中输入命令:chmod 777 HPS_FPGA_LED。然后,输入命令:./HPS_FPGA_LED执行可执行文件。

按下键盘的:Ctrl + C可以终止程序运行。

如若内容造成侵权/违法违规/事实不符,请联系编程学习网邮箱:809451989@qq.com进行投诉反馈,一经查实,立即删除!

相关文章

- KITTI Odometry相关数据集

KITTI raw data可以复制下载链接的地址至迅雷,实测迅雷可以下载 KITTI data_odometry_gray下载地址:链接:https://pan.baidu.com/s/1ecGfOSZpfXNtif7RWikhMg 提取码:du1t KITTI data_odometry_color下载地址:链接:https://pan.baidu.com/s/1BtQUxZ6vLQJHAPmDNCNTFA 提取…...

2024/5/7 17:54:55 - 14. 深度学习——Tensorflow基础(笔记)

1、认识Tensorflow1.1 Tensorflow特点2、Tensorflow 关闭警告 import os os.environ[TF_CPP_MIN_LOG_LEVEL]=22.1 图代码 import tensorflow as tf import osos.environ[TF_CPP_MIN_LOG_LEVEL] = 2 a = tf.constant(3.0) b = tf.constant(2.0) sum = tf.add(a, b)print(sum) pr…...

2024/5/6 4:32:10 - java数组复制三种方法详解

源数组如下创建新数组,并赋值int a[] = new int[20];for (int i = 0; i < a.length; i++) {a[i] = i + 15;}三种方法如下int b[] = Arrays.copyOfRange(a, 0, 20);int c[] = Arrays.copyOf(a, 10);int d[] = new int[30];System.arraycopy(a, 10, d, 5, 10);整个代码如下每…...

2024/4/22 12:24:27 - audio报错DOMException: play() failed because the user didn‘t interact with the document first解决方案

报错原因是chrome新特性,内容大致意思是开发者不能利用手中权限去给用户造成噪音干扰,首次加载页面需要用户和audio/video进行交互需求如下 实时刷新告警列表,保证用户获取到最新告警消息,当有新的告警消息时,响警报铃 解决方案当用户首次进入页面时给提示用户启用告警铃声…...

2024/4/27 6:49:46 - TDSQL初步学习

share 模式 与 单体 模式通用规范 只使用InnoDB存储引擎【默认】,避免使用MyISAM引擎 使用utf8或utf8mb4 不在数据库中存储图片、二进制文件等大数据 提前规划好单标规模,行数和大小 对象命名要使用富有意义的英文词汇,不要使用SQL关键字和特殊字符 字段属性尽量加上NOT NUL…...

2024/4/15 15:48:13 - C Primer Plus怎样高效学?C语言大神案例值得借鉴!

天下足球我们常常听到有人争论“Python、Java、PHP......是这个世界上最好的语言”,却很少听到有人夸赞C语言,为什么呢?因为C语言实在是太太太太难了...... 为什么这么多人学不会C语言呢?因为很多人觉得用C语言作为入门语言觉得太难了,里面还有指针,回调,递归之类的操作…...

2024/4/23 12:42:40 - Bus Hound 使用指南

Bushound是一款使用起来非常方便快捷的总线数据抓取工具,在我们的测试过成当中,经常会使用它来抓取数据及传输状态用于分析。在这里以usb数据传输为例,大概介绍一下Bushound的使用方法,以及一些典型异常情况的分析。一、BusHound界面介绍打开BusHound之后,显示的是这样的界…...

2024/5/1 0:56:59 - 几种深度学习库的安装

在安装好Anaconda的前提下配置安装深度学习库。 配置清华PyPI镜像 // pip config set global.index-url https://pypi.tuna.tsinghua.edu.cn/simple几种常用的深度学习库的安装:名称 命令 备注mxnet pip install mxnet CUDA版本pytorch pip install torch == 版本 torchvision…...

2024/4/15 16:56:29 - 删除表同时创建一个相同的表命令

先删除表,然后创建一个相同的表:TRUNCATE TABLE 表名;//推荐使用 删除表所有记录,一条一条删除:delete from 表名; //效率低,不推荐使用 删除表:drop table 表名:...

2024/4/26 22:24:36 - 兼容IE浏览器

一、color颜色属性 1. 支持颜色名称、十六进制、rgb、rgba body {color: red;} //颜色名称 body {color: #aaaeds;} //十六进制 body {color: rgb(255,0,51);} //rgb body {color: rgba(255,0,0,0.7);} //最后一位0.7为透明度2. IE浏览器不支持格式 body{background: #27506c…...

2024/4/28 23:32:41 - 《C#入门详解》刘铁猛——Lesson19委托

19-19-19...

2024/5/7 20:16:26 - PySpark 中 调用 Jar 包

目录启动PySpark加载数据读取顶点的DataFrame读取边的DataFrame调用Jar包后续处理 启动PySpark pyspark2 --jars GDGraphX.jar上述 GDGraphX.jar 为 封装好的 算法 Jar 包(基于 Spark 实现) 进入如下界面 Python 3.5.6 |Anaconda custom (64-bit)| (default, Aug 26 2018, 21…...

2024/4/18 16:33:15 - JDK1.8新特性

一、Lambda表达式1、Lambda表达式简介Lambda表达式是Java SE 8中一个重要的新特性。lambda表达式允许你通过表达式来代替功能接口。lambda表达式的本质是一个匿名方。2、Lambda表达式使用前提使用Lambda必须具有且仅有一个抽象方法接口,且要求接口中有且仅有一个抽象方法。使用…...

2024/4/25 3:50:18 - 超高压SiC功率器件GENESIC的6500V碳化硅晶闸管SCR模块GA060TH65

GeneSiC是碳化硅技术的先驱者和世界领导者,同时还投资高功率硅技术。全球工业和国防系统的各大领先厂商都依赖 GeneSiC 的技术提升产品性能和能效。GeneSiC 是专注于研发、制造、销售采用 SiC 半导体为基体的优质、高性能和高温度元件。SiC半导体技术对于大功率和/或恶劣环境应…...

2024/4/28 0:27:26 - WebMvcConfigurer常用实现方法介绍

1、WebMvcConfigurer介绍WebMvcConfigurer配置类其实是Spring内部的一种配置方式,采用JavaBean的形式来代替传统的xml配置文件形式进行针对框架个性化定制,可以自定义一些Handler,Interceptor,ViewResolver,MessageConverter。基于java-based方式的spring mvc配置,需要创…...

2024/5/6 2:08:32 - 作为一名优秀的测试工程师,如何完成一份完美的测试报告

之前讨论了如何完成一次云压力测试,也介绍了如何利用睿象云旗下产品:云压力测试平台(CPT)完成云压力的测试,这次我们就来详细的介绍下测试报告。 测试报告可以说是测试工作中最重要组成部分,通过测试报告可以分析和总结最优测试结果,测试出问题后调整被测服务再继续压测…...

2024/4/15 15:48:39 - kali linux 无法使用ifconfig命令

想看一下自身网卡和ip地址信息,却发现看不了。我猜可能是网络工具没有安装。命令行输入apt-get -y install net-tools安装之后问题就解决了。...

2024/4/28 9:54:47 - 用LaTeX写学校论文的模板(三)一些设置

这页的内容就不放代码了,跟之前封面一样,只要你自己定义变量位置然后放好地方,再访入信息就ok,像我是放在abstract.tex内的,像这样。一些字体和段落的设置 学校模板要求基础行距是18磅,LaTeX中pt约等于磅,所以就设置基础行距是18磅,并且重设因子为1.0 \renewcommand{\b…...

2024/4/25 16:10:18 - iOS :runtime之关联对象

大家好,我是OB! 当我们利用runtime给分类动态添加属性,本质不是给这个对象添加成员变量,而是为这个对象创建一个关联对象,所以在我们objc_setAssociatedObject添加关联对象后,利用runtime的copyIvarList 是可以发现,根本没有创建新的成员变量的。 - (void)setName:(NSSt…...

2024/4/23 17:08:11 - linux防火墙的操作

linux防火墙操作 iptables 查看防火墙状态 service iptables status 停止防火墙 service iptables stop 启动防火墙 service iptables start 重启防火墙 service iptables restart 永久关闭防火墙 chkconfig iptables off 永久关闭后重启 chkconfig iptables on firewall 防火墙…...

2024/4/20 15:32:40

最新文章

- P8801 [蓝桥杯 2022 国 B] 最大数字

P8801 [蓝桥杯 2022 国 B] 最大数字 分析 dfs 思路:题目的意思,要让一个数最大,用贪心去考虑,从高位开始,对其进行a / b操作,使其变为9,可让该数最大 1.a 操作:1;b 操…...

2024/5/7 21:25:47 - 梯度消失和梯度爆炸的一些处理方法

在这里是记录一下梯度消失或梯度爆炸的一些处理技巧。全当学习总结了如有错误还请留言,在此感激不尽。 权重和梯度的更新公式如下: w w − η ⋅ ∇ w w w - \eta \cdot \nabla w ww−η⋅∇w 个人通俗的理解梯度消失就是网络模型在反向求导的时候出…...

2024/5/7 10:36:02 - 01背包问题 小明的背包

2.小明的背包1 - 蓝桥云课 (lanqiao.cn) #include <bits/stdc.h> using namespace std; const int N1010;//开始写的105 开小了 样例过了但最后只过了很少一部分 int n,m; int v[N],w[N]; int f[N][N];int main() {cin>>n>>m;for(int i1;i<n;i){cin>&…...

2024/5/5 8:41:06 - 前端 js 经典:字符编码详解

前言:计算机只能识别二进制,开发语言中数据类型还有数字,字母,中文,特殊符号等,都需要转化成二进制编码才能让技术机识别。 一. 编码方式 ACSLL、Unicode、utf-8、URL 编码、base64 等。 1. ACSLL 对英语…...

2024/5/4 10:30:35 - 416. 分割等和子集问题(动态规划)

题目 题解 class Solution:def canPartition(self, nums: List[int]) -> bool:# badcaseif not nums:return True# 不能被2整除if sum(nums) % 2 ! 0:return False# 状态定义:dp[i][j]表示当背包容量为j,用前i个物品是否正好可以将背包填满ÿ…...

2024/5/7 19:05:20 - 【Java】ExcelWriter自适应宽度工具类(支持中文)

工具类 import org.apache.poi.ss.usermodel.Cell; import org.apache.poi.ss.usermodel.CellType; import org.apache.poi.ss.usermodel.Row; import org.apache.poi.ss.usermodel.Sheet;/*** Excel工具类** author xiaoming* date 2023/11/17 10:40*/ public class ExcelUti…...

2024/5/6 18:40:38 - Spring cloud负载均衡@LoadBalanced LoadBalancerClient

LoadBalance vs Ribbon 由于Spring cloud2020之后移除了Ribbon,直接使用Spring Cloud LoadBalancer作为客户端负载均衡组件,我们讨论Spring负载均衡以Spring Cloud2020之后版本为主,学习Spring Cloud LoadBalance,暂不讨论Ribbon…...

2024/5/6 23:37:19 - TSINGSEE青犀AI智能分析+视频监控工业园区周界安全防范方案

一、背景需求分析 在工业产业园、化工园或生产制造园区中,周界防范意义重大,对园区的安全起到重要的作用。常规的安防方式是采用人员巡查,人力投入成本大而且效率低。周界一旦被破坏或入侵,会影响园区人员和资产安全,…...

2024/5/7 14:19:30 - VB.net WebBrowser网页元素抓取分析方法

在用WebBrowser编程实现网页操作自动化时,常要分析网页Html,例如网页在加载数据时,常会显示“系统处理中,请稍候..”,我们需要在数据加载完成后才能继续下一步操作,如何抓取这个信息的网页html元素变化&…...

2024/5/7 0:32:52 - 【Objective-C】Objective-C汇总

方法定义 参考:https://www.yiibai.com/objective_c/objective_c_functions.html Objective-C编程语言中方法定义的一般形式如下 - (return_type) method_name:( argumentType1 )argumentName1 joiningArgument2:( argumentType2 )argumentName2 ... joiningArgu…...

2024/5/7 16:57:02 - 【洛谷算法题】P5713-洛谷团队系统【入门2分支结构】

👨💻博客主页:花无缺 欢迎 点赞👍 收藏⭐ 留言📝 加关注✅! 本文由 花无缺 原创 收录于专栏 【洛谷算法题】 文章目录 【洛谷算法题】P5713-洛谷团队系统【入门2分支结构】🌏题目描述🌏输入格…...

2024/5/7 14:58:59 - 【ES6.0】- 扩展运算符(...)

【ES6.0】- 扩展运算符... 文章目录 【ES6.0】- 扩展运算符...一、概述二、拷贝数组对象三、合并操作四、参数传递五、数组去重六、字符串转字符数组七、NodeList转数组八、解构变量九、打印日志十、总结 一、概述 **扩展运算符(...)**允许一个表达式在期望多个参数࿰…...

2024/5/7 1:54:46 - 摩根看好的前智能硬件头部品牌双11交易数据极度异常!——是模式创新还是饮鸩止渴?

文 | 螳螂观察 作者 | 李燃 双11狂欢已落下帷幕,各大品牌纷纷晒出优异的成绩单,摩根士丹利投资的智能硬件头部品牌凯迪仕也不例外。然而有爆料称,在自媒体平台发布霸榜各大榜单喜讯的凯迪仕智能锁,多个平台数据都表现出极度异常…...

2024/5/7 21:15:55 - Go语言常用命令详解(二)

文章目录 前言常用命令go bug示例参数说明 go doc示例参数说明 go env示例 go fix示例 go fmt示例 go generate示例 总结写在最后 前言 接着上一篇继续介绍Go语言的常用命令 常用命令 以下是一些常用的Go命令,这些命令可以帮助您在Go开发中进行编译、测试、运行和…...

2024/5/7 0:32:51 - 用欧拉路径判断图同构推出reverse合法性:1116T4

http://cplusoj.com/d/senior/p/SS231116D 假设我们要把 a a a 变成 b b b,我们在 a i a_i ai 和 a i 1 a_{i1} ai1 之间连边, b b b 同理,则 a a a 能变成 b b b 的充要条件是两图 A , B A,B A,B 同构。 必要性显然࿰…...

2024/5/7 16:05:05 - 【NGINX--1】基础知识

1、在 Debian/Ubuntu 上安装 NGINX 在 Debian 或 Ubuntu 机器上安装 NGINX 开源版。 更新已配置源的软件包信息,并安装一些有助于配置官方 NGINX 软件包仓库的软件包: apt-get update apt install -y curl gnupg2 ca-certificates lsb-release debian-…...

2024/5/7 16:04:58 - Hive默认分割符、存储格式与数据压缩

目录 1、Hive默认分割符2、Hive存储格式3、Hive数据压缩 1、Hive默认分割符 Hive创建表时指定的行受限(ROW FORMAT)配置标准HQL为: ... ROW FORMAT DELIMITED FIELDS TERMINATED BY \u0001 COLLECTION ITEMS TERMINATED BY , MAP KEYS TERMI…...

2024/5/6 19:38:16 - 【论文阅读】MAG:一种用于航天器遥测数据中有效异常检测的新方法

文章目录 摘要1 引言2 问题描述3 拟议框架4 所提出方法的细节A.数据预处理B.变量相关分析C.MAG模型D.异常分数 5 实验A.数据集和性能指标B.实验设置与平台C.结果和比较 6 结论 摘要 异常检测是保证航天器稳定性的关键。在航天器运行过程中,传感器和控制器产生大量周…...

2024/5/7 16:05:05 - --max-old-space-size=8192报错

vue项目运行时,如果经常运行慢,崩溃停止服务,报如下错误 FATAL ERROR: CALL_AND_RETRY_LAST Allocation failed - JavaScript heap out of memory 因为在 Node 中,通过JavaScript使用内存时只能使用部分内存(64位系统&…...

2024/5/7 0:32:49 - 基于深度学习的恶意软件检测

恶意软件是指恶意软件犯罪者用来感染个人计算机或整个组织的网络的软件。 它利用目标系统漏洞,例如可以被劫持的合法软件(例如浏览器或 Web 应用程序插件)中的错误。 恶意软件渗透可能会造成灾难性的后果,包括数据被盗、勒索或网…...

2024/5/6 21:25:34 - JS原型对象prototype

让我简单的为大家介绍一下原型对象prototype吧! 使用原型实现方法共享 1.构造函数通过原型分配的函数是所有对象所 共享的。 2.JavaScript 规定,每一个构造函数都有一个 prototype 属性,指向另一个对象,所以我们也称为原型对象…...

2024/5/7 11:08:22 - C++中只能有一个实例的单例类

C中只能有一个实例的单例类 前面讨论的 President 类很不错,但存在一个缺陷:无法禁止通过实例化多个对象来创建多名总统: President One, Two, Three; 由于复制构造函数是私有的,其中每个对象都是不可复制的,但您的目…...

2024/5/7 7:26:29 - python django 小程序图书借阅源码

开发工具: PyCharm,mysql5.7,微信开发者工具 技术说明: python django html 小程序 功能介绍: 用户端: 登录注册(含授权登录) 首页显示搜索图书,轮播图࿰…...

2024/5/7 0:32:47 - 电子学会C/C++编程等级考试2022年03月(一级)真题解析

C/C++等级考试(1~8级)全部真题・点这里 第1题:双精度浮点数的输入输出 输入一个双精度浮点数,保留8位小数,输出这个浮点数。 时间限制:1000 内存限制:65536输入 只有一行,一个双精度浮点数。输出 一行,保留8位小数的浮点数。样例输入 3.1415926535798932样例输出 3.1…...

2024/5/7 17:09:45 - 配置失败还原请勿关闭计算机,电脑开机屏幕上面显示,配置失败还原更改 请勿关闭计算机 开不了机 这个问题怎么办...

解析如下:1、长按电脑电源键直至关机,然后再按一次电源健重启电脑,按F8健进入安全模式2、安全模式下进入Windows系统桌面后,按住“winR”打开运行窗口,输入“services.msc”打开服务设置3、在服务界面,选中…...

2022/11/19 21:17:18 - 错误使用 reshape要执行 RESHAPE,请勿更改元素数目。

%读入6幅图像(每一幅图像的大小是564*564) f1 imread(WashingtonDC_Band1_564.tif); subplot(3,2,1),imshow(f1); f2 imread(WashingtonDC_Band2_564.tif); subplot(3,2,2),imshow(f2); f3 imread(WashingtonDC_Band3_564.tif); subplot(3,2,3),imsho…...

2022/11/19 21:17:16 - 配置 已完成 请勿关闭计算机,win7系统关机提示“配置Windows Update已完成30%请勿关闭计算机...

win7系统关机提示“配置Windows Update已完成30%请勿关闭计算机”问题的解决方法在win7系统关机时如果有升级系统的或者其他需要会直接进入一个 等待界面,在等待界面中我们需要等待操作结束才能关机,虽然这比较麻烦,但是对系统进行配置和升级…...

2022/11/19 21:17:15 - 台式电脑显示配置100%请勿关闭计算机,“准备配置windows 请勿关闭计算机”的解决方法...

有不少用户在重装Win7系统或更新系统后会遇到“准备配置windows,请勿关闭计算机”的提示,要过很久才能进入系统,有的用户甚至几个小时也无法进入,下面就教大家这个问题的解决方法。第一种方法:我们首先在左下角的“开始…...

2022/11/19 21:17:14 - win7 正在配置 请勿关闭计算机,怎么办Win7开机显示正在配置Windows Update请勿关机...

置信有很多用户都跟小编一样遇到过这样的问题,电脑时发现开机屏幕显现“正在配置Windows Update,请勿关机”(如下图所示),而且还需求等大约5分钟才干进入系统。这是怎样回事呢?一切都是正常操作的,为什么开时机呈现“正…...

2022/11/19 21:17:13 - 准备配置windows 请勿关闭计算机 蓝屏,Win7开机总是出现提示“配置Windows请勿关机”...

Win7系统开机启动时总是出现“配置Windows请勿关机”的提示,没过几秒后电脑自动重启,每次开机都这样无法进入系统,此时碰到这种现象的用户就可以使用以下5种方法解决问题。方法一:开机按下F8,在出现的Windows高级启动选…...

2022/11/19 21:17:12 - 准备windows请勿关闭计算机要多久,windows10系统提示正在准备windows请勿关闭计算机怎么办...

有不少windows10系统用户反映说碰到这样一个情况,就是电脑提示正在准备windows请勿关闭计算机,碰到这样的问题该怎么解决呢,现在小编就给大家分享一下windows10系统提示正在准备windows请勿关闭计算机的具体第一种方法:1、2、依次…...

2022/11/19 21:17:11 - 配置 已完成 请勿关闭计算机,win7系统关机提示“配置Windows Update已完成30%请勿关闭计算机”的解决方法...

今天和大家分享一下win7系统重装了Win7旗舰版系统后,每次关机的时候桌面上都会显示一个“配置Windows Update的界面,提示请勿关闭计算机”,每次停留好几分钟才能正常关机,导致什么情况引起的呢?出现配置Windows Update…...

2022/11/19 21:17:10 - 电脑桌面一直是清理请关闭计算机,windows7一直卡在清理 请勿关闭计算机-win7清理请勿关机,win7配置更新35%不动...

只能是等着,别无他法。说是卡着如果你看硬盘灯应该在读写。如果从 Win 10 无法正常回滚,只能是考虑备份数据后重装系统了。解决来方案一:管理员运行cmd:net stop WuAuServcd %windir%ren SoftwareDistribution SDoldnet start WuA…...

2022/11/19 21:17:09 - 计算机配置更新不起,电脑提示“配置Windows Update请勿关闭计算机”怎么办?

原标题:电脑提示“配置Windows Update请勿关闭计算机”怎么办?win7系统中在开机与关闭的时候总是显示“配置windows update请勿关闭计算机”相信有不少朋友都曾遇到过一次两次还能忍但经常遇到就叫人感到心烦了遇到这种问题怎么办呢?一般的方…...

2022/11/19 21:17:08 - 计算机正在配置无法关机,关机提示 windows7 正在配置windows 请勿关闭计算机 ,然后等了一晚上也没有关掉。现在电脑无法正常关机...

关机提示 windows7 正在配置windows 请勿关闭计算机 ,然后等了一晚上也没有关掉。现在电脑无法正常关机以下文字资料是由(历史新知网www.lishixinzhi.com)小编为大家搜集整理后发布的内容,让我们赶快一起来看一下吧!关机提示 windows7 正在配…...

2022/11/19 21:17:05 - 钉钉提示请勿通过开发者调试模式_钉钉请勿通过开发者调试模式是真的吗好不好用...

钉钉请勿通过开发者调试模式是真的吗好不好用 更新时间:2020-04-20 22:24:19 浏览次数:729次 区域: 南阳 > 卧龙 列举网提醒您:为保障您的权益,请不要提前支付任何费用! 虚拟位置外设器!!轨迹模拟&虚拟位置外设神器 专业用于:钉钉,外勤365,红圈通,企业微信和…...

2022/11/19 21:17:05 - 配置失败还原请勿关闭计算机怎么办,win7系统出现“配置windows update失败 还原更改 请勿关闭计算机”,长时间没反应,无法进入系统的解决方案...

前几天班里有位学生电脑(windows 7系统)出问题了,具体表现是开机时一直停留在“配置windows update失败 还原更改 请勿关闭计算机”这个界面,长时间没反应,无法进入系统。这个问题原来帮其他同学也解决过,网上搜了不少资料&#x…...

2022/11/19 21:17:04 - 一个电脑无法关闭计算机你应该怎么办,电脑显示“清理请勿关闭计算机”怎么办?...

本文为你提供了3个有效解决电脑显示“清理请勿关闭计算机”问题的方法,并在最后教给你1种保护系统安全的好方法,一起来看看!电脑出现“清理请勿关闭计算机”在Windows 7(SP1)和Windows Server 2008 R2 SP1中,添加了1个新功能在“磁…...

2022/11/19 21:17:03 - 请勿关闭计算机还原更改要多久,电脑显示:配置windows更新失败,正在还原更改,请勿关闭计算机怎么办...

许多用户在长期不使用电脑的时候,开启电脑发现电脑显示:配置windows更新失败,正在还原更改,请勿关闭计算机。。.这要怎么办呢?下面小编就带着大家一起看看吧!如果能够正常进入系统,建议您暂时移…...

2022/11/19 21:17:02 - 还原更改请勿关闭计算机 要多久,配置windows update失败 还原更改 请勿关闭计算机,电脑开机后一直显示以...

配置windows update失败 还原更改 请勿关闭计算机,电脑开机后一直显示以以下文字资料是由(历史新知网www.lishixinzhi.com)小编为大家搜集整理后发布的内容,让我们赶快一起来看一下吧!配置windows update失败 还原更改 请勿关闭计算机&#x…...

2022/11/19 21:17:01 - 电脑配置中请勿关闭计算机怎么办,准备配置windows请勿关闭计算机一直显示怎么办【图解】...

不知道大家有没有遇到过这样的一个问题,就是我们的win7系统在关机的时候,总是喜欢显示“准备配置windows,请勿关机”这样的一个页面,没有什么大碍,但是如果一直等着的话就要两个小时甚至更久都关不了机,非常…...

2022/11/19 21:17:00 - 正在准备配置请勿关闭计算机,正在准备配置windows请勿关闭计算机时间长了解决教程...

当电脑出现正在准备配置windows请勿关闭计算机时,一般是您正对windows进行升级,但是这个要是长时间没有反应,我们不能再傻等下去了。可能是电脑出了别的问题了,来看看教程的说法。正在准备配置windows请勿关闭计算机时间长了方法一…...

2022/11/19 21:16:59 - 配置失败还原请勿关闭计算机,配置Windows Update失败,还原更改请勿关闭计算机...

我们使用电脑的过程中有时会遇到这种情况,当我们打开电脑之后,发现一直停留在一个界面:“配置Windows Update失败,还原更改请勿关闭计算机”,等了许久还是无法进入系统。如果我们遇到此类问题应该如何解决呢࿰…...

2022/11/19 21:16:58 - 如何在iPhone上关闭“请勿打扰”

Apple’s “Do Not Disturb While Driving” is a potentially lifesaving iPhone feature, but it doesn’t always turn on automatically at the appropriate time. For example, you might be a passenger in a moving car, but your iPhone may think you’re the one dri…...

2022/11/19 21:16:57