Verilog学习笔记(06)

文章目录

- 7. 时序逻辑电路

- 1.触发器

- (1)D触发器

- (2)JK触发器

- (3)T触发器

- 2. 移位寄存器

- (1)右移寄存器

- (2)左移寄存器

- 3. 计数器

- (1)反馈清零计数器

- (2)反馈置数计数器

- (3)移位计数器

- 4. 信号产生器

- (1)状态图类型

- (2)移位寄存器类型

- (3)计数器加组合输出网络类型

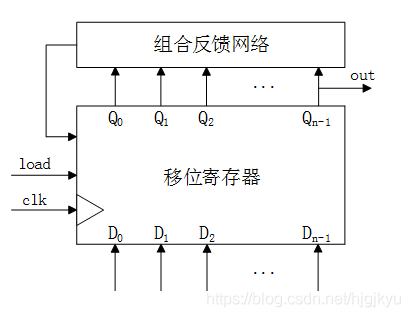

- (4)移位寄存器加组合逻辑反馈电路类型

- (5)m序列信号发生器

- 5. 有限状态机

- (1)状态机的组成

- (2)状态机分类

- (3)状态机的编码方式

- (4)有限状态机的设计方式

参考:Verilog数字VLSI设计教程

硬件描述语言Verilog

Verilog HDL数字设计与综合

Verilog HDL 数字集成电路高级程序设计

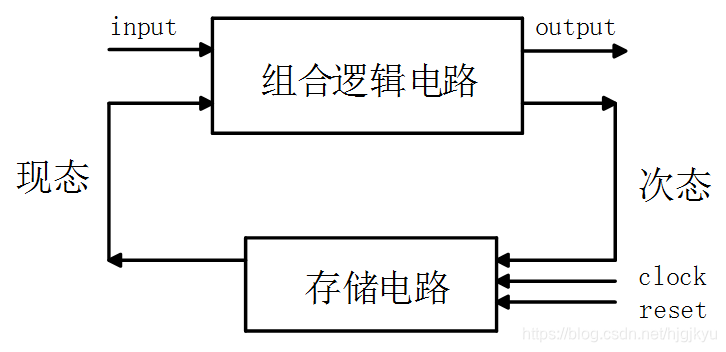

7. 时序逻辑电路

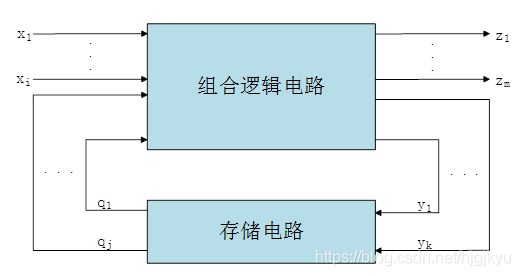

对于一个时序电路,可以把它分为一部分组合逻辑和一部分存储逻辑

时序电路的三大方程

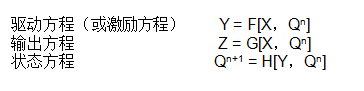

典型的时序电路设计流程

1.触发器

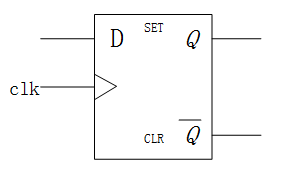

(1)D触发器

module dff(clk,clr,rst,d,q);

input clk,clr,rst,d;

output q;

reg q;

always @(posedge clk or posedge clr)

if(clr==1'b1) q<=1'b0;

else if(rst==1'b1) q<=1'b1;

else q<=d;

endmodule

module dff_tb;reg clk,clr,rst,d;wire q;always begin#10 clk=1'b1;#10 clk=1'b0;endinitial beginclk=1'b0;clr=1'b0;rst=1'b0;clr=1'b0;d=1'b0;#10 rst=1'b1;clr=1'b0;d=1'b0;#10 clr=1'b1;rst=1'b1;d=1'b1;#10 clr=1'b0;rst=1'b0;d=1'b1;#20 d=1'b0;#20 d=1'b1;end

dff u1(clk,clr,rst,d,q);

endmodule

8位D触发器

module eight_register(d,clk,q);

input [7:0] d;

input clk;

output [7:0] q;

reg [7:0] q;

always @(posedge clk) q<=d;

endmodule

module dff8_tb;reg [7:0] d;reg clk;wire [7:0] q;always begin#10 clk=1'b1;#10 clk=1'b0;endinitial beginclk=1'b0;d=8'b00000000; #10 d=8'b00000011;#10 d=8'b00000000;#10 d=8'b00000111;#20 d=8'b00001111;#20 d=8'b00011111;#20 d=8'b00111111;end

dff8 u1(.d(d),.clk(clk),.q(q));

endmodule

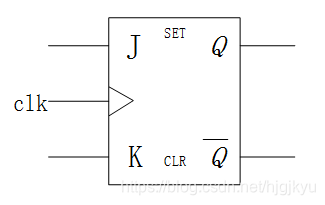

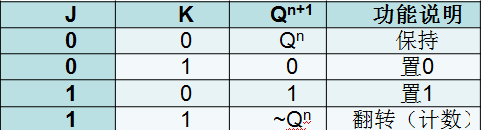

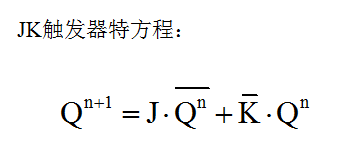

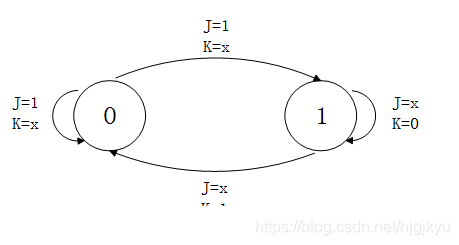

(2)JK触发器

module jk_trigger(clk,j,k,q,qb);

input clk,j,k;

output q,qb;

reg q;

always@(posedge clk)

begin

case({j,k})

2'b00:q<=q;

2'b01:q<=1'b0;

2'b10:q<=1'b1;

2'b11:q<=~q;

default: q<=q;

endcase

end

assign qb=~q;

endmodule

module jk_trigger_tb;

reg clk,j,k;

wire q,qb;always begin#10 clk=1'b1;#10 clk=1'b0;endinitial beginclk=1'b0;j=1'b0;k=1'b0;#10 j=1'b0;k=1'b0;#20 j=1'b0;k=1'b1;#20 j=1'b1;k=1'b0;#20 j=1'b1;k=1'b1;#20 j=1'b1;k=1'b0;endjk_trigger u1(clk,j,k,q,qb);endmodule

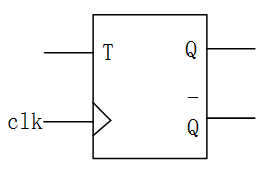

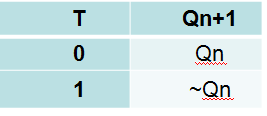

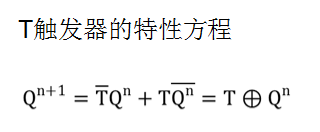

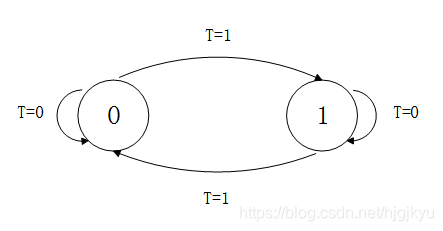

(3)T触发器

module t_trigger(clk,rst,T,dout);

input clk,rst,T;

output dout;

reg dout;

always @(posedge clk or posedgerst)

if(rst==1) dout<=1'b0;

else if(T==1) dout<=~dout;

endmodule

module t_trigger_tb;reg clk,rst,T;wire dout;always begin#10 clk=1'b1;#10 clk=1'b0;endinitial begin clk=1'b0;rst=1'b0;T=1'b0;#10 rst=1'b1;T=1'b1;#10 rst=1'b0;T=1'b0;#20 T=1'b1;#20 T=1'b0;#20 T=1'b1;end

t_trigger u1(clk,rst,T,dout);

endmodule

2. 移位寄存器

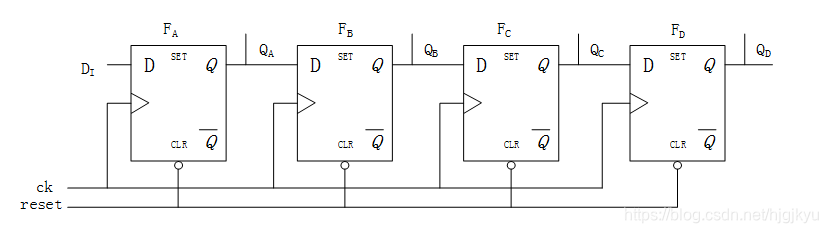

(1)右移寄存器

module register_right(clk,din,dout);

input clk;

input din;

output [15:0] dout;

reg [15:0] dout;

always @(posedge clk)

dout<={din,dinout[15:1]};

endmodule

module register_right_tb;

reg clk;

reg din;

wire [15:0] dout;always begin#10 clk=1'b1;#10 clk=1'b0;endinitial beginclk=1'b0;din=1'b0;#10 din=1'b1;#20 din=1'b0;#20 din=1'b1;#100;end

register_right u1(clk,din,dout);

endmodule

(2)左移寄存器

module register_left(clk,din,dout);

input clk;

input [15:0] din;

output [15:0] dout;

reg [15:0] dout;

always @(posedge clk)

dout<={din[14:0],din[15]};

endmodule

module register_left_tb;

reg clk;

reg [15:0] din;

wire [15:0] dout;always begin#10 clk=1'b1;#10 clk=1'b0;endinitial beginclk=1'b0;din=16'b0000000000000000;#10 din=16'b0000000000000001;#20 din=16'b0000000000000011;#20 din=16'b0000000000000101;end

register_left u1(clk,din,dout);

endmodule

3. 计数器

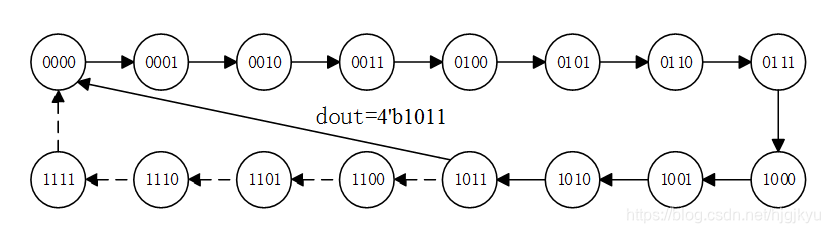

(1)反馈清零计数器

module count12(clk,rst_n,co,dout);

input clk,rst;

output co;

output [3:0] dout;

reg [3:0] dout;

always @ (posedge clk)

begin

if(rst_n==1'b0) dout=4'b0000;

else if(dout==4'b1011) dout<=4'b0000;

else dout<=dout+1'b1;

end

assign co=dout[3]&&dout[1]&&dout[0];

endmodule

module count12_tb;

reg clk,rst_n;

wire oc;

wire [3:0] dout;

always begin#10 clk=1'b1;#10 clk=1'b0;end

initial beginclk=1'b0;rst_n=1'b0; #20 rst_n=1'b1;#100;end

count12 u1(clk,rst_n,oc,dout);

endmodule

(2)反馈置数计数器

module count10(clk,rst,load,din,dout);

input clk,rst,load;

input [3:0] din;

output [3:0] dout;

reg [3:0] dout;

always @ (posedge clk or posedge rst)

begin

if(rst==1'b1) dout=4'b0000;

else if(load==1'b 1) dout=4'b1001;

else if(dout==4'b0000) dout<=4'b1001;

else dout<=dout-1'b1;

end

endmodule

module count10_tb;

reg clk,rst,load;

reg [3:0] din;

wire [3:0] dout;

always begin#10 clk=1'b1;#10 clk=1'b0;endinitial begin clk=1'b0;rst=1'b0;load=1'b0; #10 rst=1'b1;#10 rst=1'b0;#50 load=1'b1;#10 load=1'b0;#100;end

count10 u1(clk,rst,load,din,dout);

endmodule

(3)计数器级联

module count10(clk,rst_n,en,dout,co);

input clk,rst_n,en;

output[3:0] dout;

output co;

reg [3:0] dout;

always @ (posedge clk or negedge rst_n)

begin

if(rst_n ==1'b 0) dout<=4'b0000;

else if(en==1'b1)

if(dout==4'b1001) dout<=4'b0000;

else dout<=dout+1'b1;

else dout<=dout;

end

assign co=dout[0]&dout[3];

endmodule

module count6(clk,rst_n,en,dout,co);

input clk,rst_n,en;

output[3:0] dout;

output co;

reg [3:0] dout;

always @ (posedge clk or negedge rst_n)

begin

if(rst_n ==1'b 0) dout<=4'b0000;

else if(en==1'b1)

if(dout==4'b0101) dout<=4'b0000;

else dout<=dout+1'b1;

else dout<=dout;

end

assign co=dout[0]&dout[2];

endmodule

module count60(clk,rst_n,en,dout,co);

input clk,rst,en;

output[7:0] dout;

output co;

wire c010,co6;

wire[3:0] dout10,dout6;

counter_10 u1(.clk(clk),.rst_n(rst_n),.en(en),.dout(dout10),.co(co10));counter_6 u2(.clk(clk),.rst_n(rst_n),.en(co10),.dout(dout6),.co(co6));and u3(co,co10,co6);assign dout={dout6,dout10};

endmodule

module count60_tb ;reg clk,rst_n,en ;wire [7:0] dout ;wire co ;always begin#1 clk=1'b1 ;#1 clk=1'b0 ;endinitialbeginclk=1'b0 ;rst_n=1'b1 ;en=1'b1;#1 rst_n=1'b0 ;#1 rst_n=1'b1 ;endcount60 U1(.clk(clk),.rst_n(rst_n),.en(en),.dout(dout),.co(co));

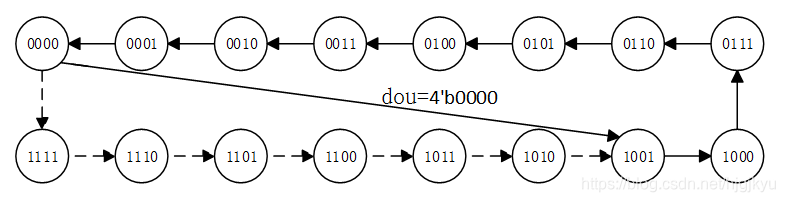

endmodule (3)移位计数器

扭环计数器

module twisted_counter(clk,rst_n,dout);

input clk,rst_n;

output[3:0] dout;

reg [3:0] dout;

always @(posedge clk or negedge rst_n)

if(!rst_n) dout<=4'b0000;

else begin

dout<={dout[2:0],~dout[3] };

endmodule

module twisted_counter_tb;

reg clk,rst_n;

wire [3:0] dout;

always begin#10 clk=1'b1;#10 clk=1'b0;endinitial beginclk=1'b0;rst_n=1'b1;#10 rst_n=1'b0;#10 rst_n=1'b1;#100;end

twisted_counter u1(clk,rst_n,dout);

endmodule

4. 信号产生器

(1)最大循环长度序列码,M=2n。

(2)最长线形序列码(m序列码),M=2n-1。

(3)任意循环长度序列码,M<2n。

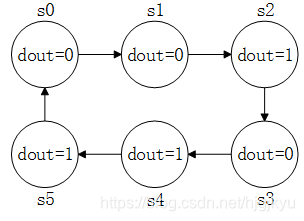

(1)状态图类型

有限状态机方式实现001011序列信号产生器

module sequence_signal_fsm(clk,rst_n,dout);input clk,rst_n;output dout;reg dout;reg [2:0] pre_state,next_state;parameter s0=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100,s5=3'b101;always @(posedge clk or negedge rst_n)if(rst_n ==1'b0) pre_state<=s0;else pre_state<=next_state;always @(pre_state)case(pre_state)s0:begin dout<=1'b0;next_state<=s1;ends1:begin dout<=1'b0;next_state<=s2;ends2:begin dout<=1'b1;next_state<=s3;ends3:begin dout<=1'b0;next_state<=s4;ends4:begin dout<=1'b1;next_state<=s5;ends5:begin dout<=1'b1;next_state<=s0;enddefault next_state<=s0;endcase

endmodule

module sequence_signal_fsm_tb;reg clk,rst_n;wire dout;sequence_signal_fsm u1(clk,rst_n,dout);always #10 clk=~clk;initialbeginclk=1'b0;rst_n=1'b1;#5 rst_n=1'b0;#5 rst_n=1'b1;end

endmodule

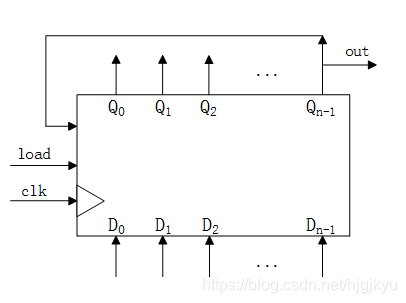

(2)移位寄存器类型

移位寄存器型序列信号产生器

module signal_generator_shifter_reg(clk,rst,din,dout);

input clk,rst;

input [5:0] din;

output dout;

reg dout;

reg [5:0] temp;

always @(posedge clk)

begin

if(rst==1'b1) temp<=din;

else begin

dout<=temp[5];

temp<={temp[4:0],temp[5]};

end

end

endmodule

module signal_generator_shifter_reg_tb;reg clk,rst;reg [5:0] din;wire dout;signal_generator_shifter_reg u1(.clk(clk),.rst(rst),.din(din),.dout(dout));always #10 clk=~clk;initial beginclk=1'b0;rst=1'b0;#10 rst=1'b1;din=6'b001011;#20 rst=1'b0;end

endmodule

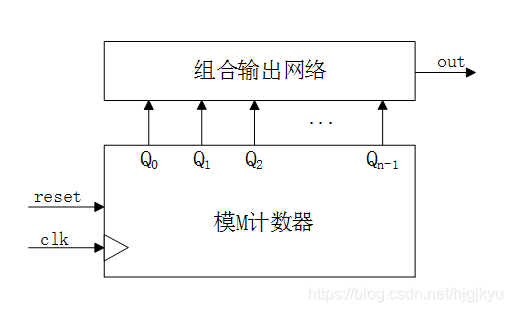

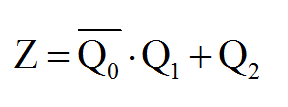

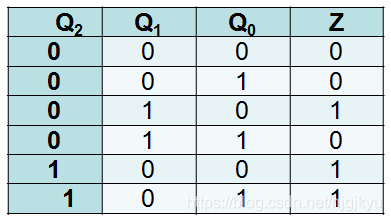

(3)计数器加组合输出网络类型

计数器+组合编码电路 001011序列信号产生器。

module counter_sequence(clk,rst,dout);

input clk,rst;

output dout;

reg [2:0] counter;

always @(posedge clk)

if(rst==1'b1)counter<=3'b000;

else if(counter==3'b101) counter<=3'b000;

else counter<=counter+1'b1;

assign dout=((~counter[0])&counter[1])|counter[2];

endmodule

module counter_sequence_tb;reg clk,rst;wire dout;counter_sequence u1(.clk(clk),.rst(rst),.dout(dout));always #10 clk=~clk;initialbeginclk=1'b0;rst=1'b0;#10 rst=1'b1;#20 rst=1'b0;end

endmodule

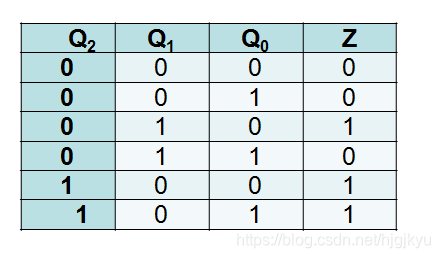

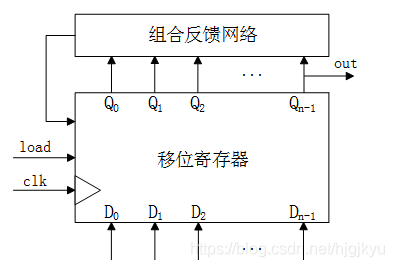

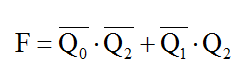

(4)移位寄存器加组合逻辑反馈电路类型

(1)根据给定的序列信号的循环长度M,确定寄存器位数n,2n-1<M≤2n。

(2)确定移位寄存器的M个独立状态。

将给定的序列码按照移位规律每n位一组,划分为M个状态。若M个状态中出现重复现象,则应增加移位寄存器位数。用n+1位再重复上述过程,直到划分为M个独立状态为止。

(3)根据M个不同的状态列出移位寄存器的态序表和反馈函数表,求出反馈函数F的表达式。

(4)检查自启动性能。

设计一个移位寄存器加组合逻辑电路类型的010011序列信号发生器。

对于“010011”序列的信号发生器

module signal_shifter_feedback(clk,load,dout,D);

input clk,load;

input [2:0]D;

output dout;

reg [2:0] Q;

wire F;

always @(posedge clk)

if(load==1'b1) Q<=D;

else Q<={Q[1:0],F};

assign F=((~Q[0])&(~Q[2]))|((~Q[1])&Q[2]);

assign dout=Q[2];

endmodule

module signal_shifter_feedback_tb;reg clk,load;reg[2:0] D;wire dout;signal_shifter_feedback u1(.clk(clk),.load(load),.dout(dout),.D(D));always #10 clk=~clk;initialbeginclk=1'b0;D=3'b001;load=1'b0;#10 load=1'b1;#20 load=1'b0;end

endmodule

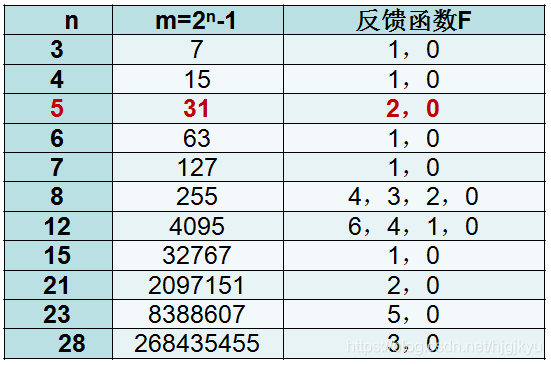

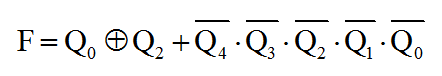

(5)m序列信号发生器

设计一个m序列信号产生器的Verilog HDL描述,该程序中n=5

module m_sequence(clk,en,dout,D);

input clk,en;

input[4:0] D;

output dout;

reg[4:0] Q;

wire F;

always @ (posedge clk)

if(en==1'b0) Q<=D;

else Q<={Q[3:0],F};

assign F=(Q[0]^Q[2])|((~Q[4])&(~Q[3])&(~Q[2])&(~Q[1])&(~Q[0]));

assign dout=Q[4];

endmodule

module m_sequence_tb;reg clk,en;reg[4:0] D;wire dout;m_sequence u1(.clk(clk),.en(en),.dout(dout),.D(D));always #10 clk=~clk;initialbeginclk=1'b0;D=5'b10000;en=1'b0;#20 en=1'b1;end

endmodule

5. 有限状态机

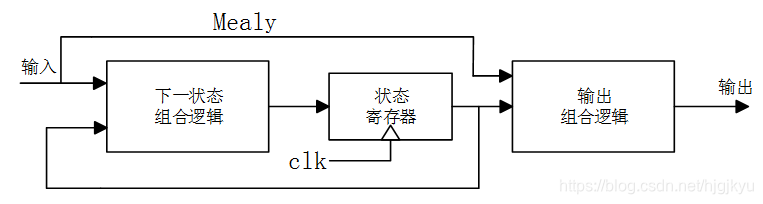

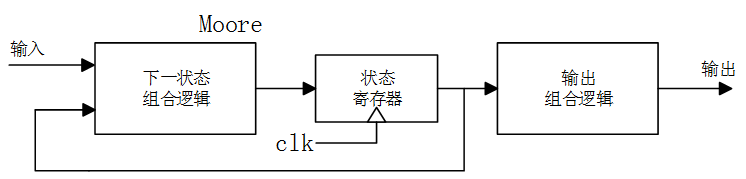

(1)状态机的组成

(2)状态机分类

Mealy型

Moore型

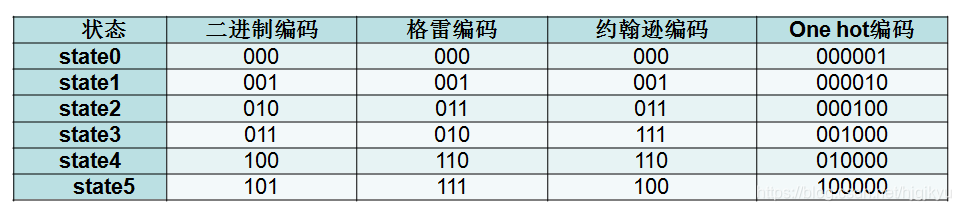

(3)状态机的编码方式

(4)有限状态机的设计方式

用两段式描述的5进制同步加法计数器

module couter5_fsm(clk,rst_n,Z);input clk,rst_n;utput Z;reg Z;reg[2:0] pre_state,next_state;parameter s0=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100;//第一个过程,同步时序always模块,描述状态转移方程

always @(posedge clk or negedge rst_n)if(!rst_n) pre_state<=s0;else pre_state<=next_state;//第二个过程,组合逻辑always模块,描述激励方程和输出方程

always @(pre_state)beginnext_state=3'bxxx;Z=1'b0;case (pre_state)s0:beginnext_state=s1;Z=1'b0;ends1:beginnext_state=s2;Z=1'b0;ends2:beginnext_state=s3;Z=1'b0;ends3:beginnext_state=s4;Z=1'b0;ends4:beginnext_state=s0;Z=1'b1;enddefault:beginnext_state=s0;endendcaseendendmodule

用三段式描述5进制加法计数器

module couter5_fsm(clk,rst_n,Z);input clk,rst_n;output Z;reg Z;reg[2:0] pre_state,next_state;parameter s0=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100;//第一个过程,同步时序always模块,描述状态转移方程

always @(posedge clk or negedge rst_n)if(!rst_n) pre_state<=s0;elsepre_state<=next_state;//第二个过程,组合逻辑always模块,描述激励方程

always @(pre_state)beginnext_state=3'bxxx;case (pre_state)s0:next_state=s1;s1:next_state=s2;s2:next_state=s3;s3:next_state=s4;s4:next_state=s0;default:next_state=s0;endcaseend//第三个过程,同步时序always模块,格式化描述输出方程

always @(pre_state)beginZ=1'b0;case (pre_state)s0: Z=1'b0;s1: Z=1'b0;s2: Z=1'b0;s3: Z=1'b0;s4: Z=1'b1;default: Z=1'b0;endcaseendendmodule

module couter5_fsm_tb;

reg clk,rst_n;

wire Z;

couter5_fsm u1(clk,rst_n,Z);

always #10 clk=~clk;initialbeginclk=1'b0;rst_n=1'b1;#10 rst_n=1'b0;#10 rst_n=1'b1;end

endmodule

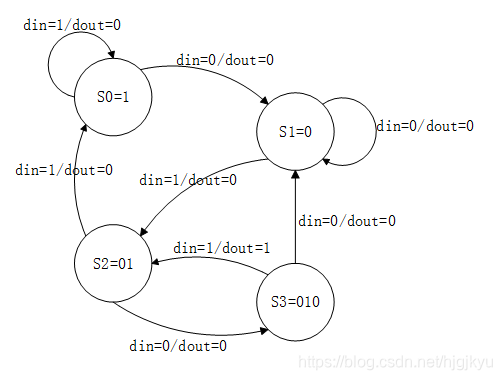

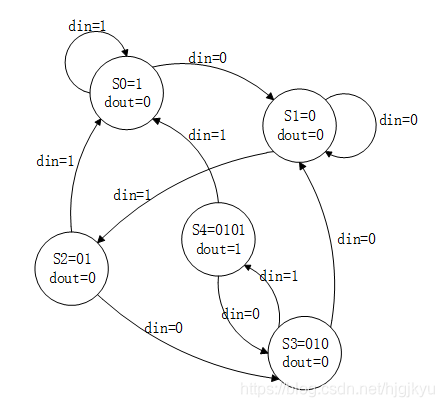

设计Mealy型0101序列检测器。

module detector_Mealy(clk,rst_n,din,dout);input clk,rst_n,din;output dout;reg dout;reg [1:0] pr_state,next_state;parameter s0=2'b00,s1=2'b01,s2=2'b10,s3=2'b11;always @(posedge clk or negedge rst_n)beginif(rst_n ==1'b0) pr_state<=s0;else pr_state<=next_state;endalways@(pr_state or din)beginnext_state<=2'bxx;dout<=1'b0;case(pr_state)s0: //the state is 1;beginif(din==1'b1) begin next_state<=s0; dout<=1'b0;endelse begin next_state<=s1; dout<=1'b0;endends1://the state is 0;beginif(din==1'b1) beginnext_state<=s2; dout<=1'b0;endelse next_state<=s1;ends2: //the state is 01;beginif(din==1'b1) beginnext_state<=s0; dout<=1'b0;endelse next_state<=s3; ends3: //the state is 010; beginif(din==1'b1) beginnext_state<=s2; dout<=1'b1;endelsenext_state<=s1;endendcaseend

endmodule

module detector_Mealy_tb;reg clk,rst_n,din;wire dout;detector_Mealy u1(.clk(clk),.rst_n(rst_n),.din(din),.dout(dout));always #50 clk=~clk;initialbeginclk=1'b1;rst_n=1'b0;#100 rst_n=1'b1; din=1'b0;#100 din=1'b0;#100 din=1'b1;#100 din=1'b0;#100 din=1'b1;#100 din=1'b0;#100 din=1'b0;#100 din=1'b0;#100 din=1'b1;#100 din=1'b0;#100 din=1'b1;#100 din=1'b0;#100 din=1'b1;#100 din=1'b0;end

endmodule

用Moore型状态机实现0101序列检测器

module detector_Moore(clk,rst_n,din,dout);input clk,rst_n,din;output dout;reg dout;reg [2:0] pr_state,next_state;parameter s0=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100;always @(posedge clk or negedge rst_n) beginif(rst_n ==1'b0) pr_state<=s0; else pr_state<=next_state; endalways@(pr_state or din) beginnext_state<=2'bxx; dout<=1'b0; case(pr_state) s0://the state is 1;begindout<=1'b0;if(din==1'b1) next_state<=s0;else next_state<=s1; ends1://the state is 0; begindout<=1'b0;if(din==1'b1)next_state<=s2;else next_state<=s1;s2: //the state is 01;begindout<=1'b0;if(din==1'b1)next_state<=s0;else next_state<=s3; ends3: //the state is 010; begindout<=1'b0;if(din==1'b1)next_state<=s4; else next_state<=s1;ends4: //the state is 0101;begindout<=1'b1;if(din==1'b1) next_state<=s0;else next_state<=s3;endendcaseendendmodule

module detector_Moore_tb;reg clk,rst_n,din;wire dout;detector_Moore u1(.clk(clk),.rst_n(rst_n),.din(din),.dout(dout));always #50 clk=~clk;initialbeginclk=1'b1;rst_n=1'b0;#100 rst_n=1'b1; din=1'b0;#100 din=1'b0;#100 din=1'b1;#100 din=1'b0;#100 din=1'b1;#100 din=1'b0;#100 din=1'b0;#100 din=1'b0;#100 din=1'b1;#100 din=1'b0;#100 din=1'b1;#100 din=1'b0;#100 din=1'b1;#100 din=1'b0;end

endmodule

计数器控制的状态机。该程序为计数器控制的状态机模型,0—16数值分别对应了不同的格雷码和约翰逊码,当计数器进行计数时,计数到每一个不同状态,相应地输出该状态所对应的格雷码和约翰逊码。

module counter_fsm(clk,rst,dout_gray,dout_johnson);

input clk,rst;

output [3:0] dout_gray;

output [7:0] dout_johnson;

reg [3:0] dout_gray;

reg [7:0] dout_johnson;

reg [3:0] counter; always @(posedge clk) if(rst==1'b1) counter=4'b0000; else counter=counter+4'b0001; always @(counter) case(counter) 4'b0000: begin dout_gray=4'b0000;dout_johnson=8'b0000_0000;end4'b0001: begin dout_gray=4'b0001; dout_johnson=8'b0000_0001;end 4'b0010: begin dout_gray=4'b0011; dout_johnson=8'b0000_0011;end 4'b0011: begin dout_gray=4'b0010;dout_johnson=8'b0000_0111;end 4'b0100: begin dout_gray=4'b0110;dout_johnson=8'b0000_1111;end 4'b0101: begin dout_gray=4'b0111;dout_johnson=8'b0001_1111;end 4'b0110: begin dout_gray=4'b0101;dout_johnson=8'b0011_1111;end 4'b0111: begin dout_gray=4'b0100;dout_johnson=8'b0111_1111;end 4'b1000: begin dout_gray=4'b1100;dout_johnson=8'b1111_1111;end 4'b1001: begin dout_gray=4'b1101;dout_johnson=8'b1111_1110;end 4'b1010: begin dout_gray=4'b1111;dout_johnson=8'b1111_1100;end 4'b1011: begin dout_gray=4'b1110;dout_johnson=8'b1111_1000;end 4'b1100: begin dout_gray=4'b1010;dout_johnson=8'b1111_0000;end 4'b1101: begin dout_gray=4'b1011;dout_johnson=8'b1110_0000;end 4'b1110: begin dout_gray=4'b1001;dout_johnson=8'b1100_0000;end 4'b1111: begin dout_gray=4'b1000;dout_johnson=8'b1000_0000;end endcaseendmodule

module counter_fsm_tb;reg clk,rst;wire [3:0] dout_gray;wire [7:0] dout_johnson;counter_fsm u1(.clk(clk),.rst(rst),.dout_gray(dout_gray),.dout_johnson(dout_johnson));always #10 clk=~clk;initialbeginclk=1'b0;rst=1'b0;#10 rst=1'b1;#20 rst=1'b0;end

endmodule

如若内容造成侵权/违法违规/事实不符,请联系编程学习网邮箱:809451989@qq.com进行投诉反馈,一经查实,立即删除!

相关文章

- yii资料集191128

Yii 2.0 权威指南 | Yii PHP Framework https://www.yiiframework.com/doc/guide/2.0/zh-cn Yii2 干货集 (https://github.com/forecho/awesome-yii2)yii自带rbac数据表分析(https://blog.csdn.net/m_422744746/article/details/52889928)yii pageTitle与Yii::app()->name …...

2024/4/20 17:32:57 - scrollTop、scrollLeft、scrollWidth、scrollHeight原理使用介绍

上面是一个网页,由于窗口大限的限制,没有完全显示出来,没有显示出来的,用阴影标注了。 上阴影就是 scrollTop;上阴影 + 白的 + 下阴影就是 scrollHeight。scrollTop 是“卷”起来的高度值,示例: <div style="width:200px;height:200px;background-color:#999999…...

2024/5/1 16:06:40 - Python中的subprocess

看python的document 自个慢慢琢磨~~,每天花一点时间学习。某某人说要厚积薄发! 先看看subprocess是干什么用的:The subprocess modul allows you to spawn new processes, connect to their input/output/error pipes, and obtain their return codes.即启用另一个线程,并可…...

2024/4/20 12:41:38 - 微信分享android成功,ios失败

看页面链接是不是https开头的,是的话就要引入https的js文件而不是以http开头<script src="https://res.wx.qq.com/open/js/jweixin-1.2.0.js"></script>url参数中带了中文字符,要将其encodeURIComponent()编码ar content = {title: 您的好友邀请你办信…...

2024/4/17 21:09:35 - 开源的B2B网站 及 B2B、B2C、C2C的讲解

Satchmo, the django based ecommerce framework: http://www.satchmoproject.com/.大家纯搞技术了,B2B、B2C、C2C都没搞明白就回信。 B是商家 C是用户 B2B,就是商家搞商家;比如,阿里巴巴,慧聪 B2C,就是商家搞用户;比如,亚马逊,(淘宝商城也算B2C) C2C,就是用…...

2024/4/17 20:55:20 - python subprocess.Popen 监控控制台输出

转自: http://blog.csdn.net/mldxs/article/details/8555819file_out = subprocess.Popen(ping www.baidu.com, shell=True, stdout=subprocess.PIPE, stderr=subprocess.STDOUT)while True: line = file_out.stdout.readline() print(line) if subprocess.Popen.pol…...

2024/4/14 15:45:22 - 重新开始学习FPGA

由于挖的坑,需要自己去填。需要认真学习FPGA-Verilog,在此记录我的学习过程。 学习的平台为黑金AX516开发板。 学习内容: 1、Verilog教程 2、microBlaze教程学完之后开始做项目,激光雷达的在线处理,一个人的舞台,加油...

2024/4/17 20:56:26 - git 恢复版本

composer create-project --prefer-dist fancyecommerce/fecshop-app-advancedgit log file 查看版本号 git reset --hard d756f627fe568f4d8bcf1852ba60557eeab477a5 (版本号)首先,在确认需要进行版本还原以后, 打开GIT BASH 输入:例如: git reset --hard d756f627fe568f4d…...

2024/4/17 20:54:19 - clientWidth、clientHeight、offsetWidth、offsetHeight以及scrollWidth、scrollHeight

clientWidth、clientHeight、offsetWidth、offsetHeight以及scrollWidth、scrollHeight是几个困惑了好久的元素属性,趁着有时间整理一下 1. clientWidth 和 clientHeight 网页中的每个元素都具有 clientWidth 和 clientHeight 属性,表示可视区域的宽高,即元素内容加上paddi…...

2024/5/8 20:16:51 - python subprocess.Popen 非阻塞

1、非阻塞设置subprocess.Popen(args, stdout=subprocess.PIPE,stderr=subprocess.PIPE)def non_block_read(output):fd = output.fileno()fl = fcntl.fcntl(fd, fcntl.F_GETFL)fcntl.fcntl(fd, fcntl.F_SETFL, fl | os.O_NONBLOCK)try:return output.read()except:return &quo…...

2024/5/1 19:05:45 - Verilog 按键消抖及控制蜂鸣器

参考:正点原子(http://www.openedv.com)——开拓者FPGA教程RTL原理图:top 程序://author: bronceyang //time : 2020年4月16日 //version: 1.0 //功能:按键消抖;按键控制蜂鸣器的叫停module beep_key(input sys_clk,input sys_rst_n,input key,output beep); //paramet…...

2024/4/24 10:12:04 - Nopcommerce4.2解析——安装

Nopcommerce是一个DotNet领域异常凶残的一个开源电商系统,最先版本4.2,下面我们会逐步分析他的各个模块,为我们的二次开发做准备,应该会写一个系列。 首次运行nop页面会自动跳转到安装页面,页面时怎么完成跳转的呢?首先想到的时ActionFilter,这是我们在Mvc5中的常见方案…...

2024/4/28 11:45:48 - ubuntu python subprocess模块执行python脚本

语法: import subprocess subprocess.call(python test.py,shell=True)注意当在ubuntu系统运行时,这里的shell=True不可少。...

2024/4/18 23:10:35 - FPGA和Verilog的一些资料

Bookmarks Bookmarks书签栏www.fpgadesign.cn/p/d.php?id=35Quartus II调用modelsim无缝仿真 - emouse - 博客园Quartus II和Modelsim的联合仿真(详细) - Jezze - 博客园FPGA学习手记(四)ModelSim入门及Testbench编写——合理利用仿真才是王道 - 电子懒兔 - 与非博客 - 与…...

2024/4/19 12:09:23 - subprocess子进程创建过程详解

文章目录引子shell内建命令和外部命令subprocess在Linux下执行命令subprocess在Windows下执行命令参考 引子 有一个需求:代码运行环境为python 3.7,用python获取系统所有别名信息。 首先想到的,就是使用subprocess模块创建子进程,执行alias命令并获取返回值。于是出现了这样…...

2024/4/17 21:48:40 - Android 蓝牙开发(十)A2DP源码分析

转载请注明出处:http://blog.csdn.net/vnanyesheshou/article/details/71811288本文已授权微信公众号 fanfan程序媛 独家发布 扫一扫文章底部的二维码或在微信搜索 fanfan程序媛 即可关注上一篇说了下A2DP的一些基本操作,这篇分析下系统应用、系统源码是如何操作A2DP的。尤其…...

2024/5/8 10:53:04 - Java开源生鲜电商平台-支付模块的设计与架构(源码可下载)

Java开源生鲜电商平台-支付模块的设计与架构(源码可下载)开源生鲜电商平台支付目前支持支付宝与微信。针对的是APP端(android or IOS)1. 数据库表设计说明:无论是支付宝还是微信支付,都会有一个服务端的回调,业务根据回调的结果处理相应的业务逻辑。pay_logs这个表主要是…...

2024/4/17 20:54:07 - Yii2 – Mongodb的安装和配置 mongo

mongodb官方安装文档:https://www.mongodb.com/download-center 下面是centos环境安装mongodb3.2的步骤 1. sudo rpm --import https://www.mongodb.org/static/pgp/server-3.2.asctouch /etc/yum.repos.d/mongodb-org-3.2.repovim /etc/yum.repos.d/mongodb-org-3.2.repo 添…...

2024/4/19 0:45:06 - Verilog 中定义信号为什么要区分 wire 和 reg 两种类型?

作者:young cc链接:https://www.zhihu.com/question/21021718/answer/56339195来源:知乎著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。两者差别很大,完全不能取消。在Verilog中,wire永远是wire,就是相当于一条连线,用来连接电路,不能存储数据…...

2024/5/5 18:47:48 - js 中clientHeight、offsetHeight、scrollHeight、offsetTop、scrollTop

网页可见区域高:document.body.clientHeight 网页正文全文高:document.body.scrollHeight 网页可见区域高(包括边线的高):document.body.offsetHeight 网页被卷去的高:document.body.scrollTop 屏幕分辨率高:window.screen.height 每个HTML元素都具有clientHeight offse…...

2024/5/8 2:53:14

最新文章

- 7-1 图图图

某城市有n个景点,部分景点之间有巴士免费来回接送。(1) 给定某个景点x,如果从这个景点出发坐一次免费巴士,可以到达多少个不同的景点?(2) 判断景点a是否可以通过免费巴士(可换乘)到达景点b;(3) …...

2024/5/8 22:36:30 - 梯度消失和梯度爆炸的一些处理方法

在这里是记录一下梯度消失或梯度爆炸的一些处理技巧。全当学习总结了如有错误还请留言,在此感激不尽。 权重和梯度的更新公式如下: w w − η ⋅ ∇ w w w - \eta \cdot \nabla w ww−η⋅∇w 个人通俗的理解梯度消失就是网络模型在反向求导的时候出…...

2024/5/7 10:36:02 - 鹅厂实习offer

#转眼已经银四了,你收到offer了吗# 本来都打算四月再投实习了,突然三月初被wxg捞了(一年前找日常实习投的简历就更新了下),直接冲了,流程持续二十多天,结果是运气还不错,应该是部门比…...

2024/5/1 13:19:09 - 汽车疲劳测试试验平台技术要求(北重厂家)

汽车疲劳测试试验平台技术要求通常包括以下几个方面: 车辆加载能力:测试平台需要具备足够的承载能力,能够同时测试多种车型和不同重量的车辆。 动力系统:测试平台需要具备稳定可靠的动力系统,能够提供足够的力和速度来…...

2024/5/8 14:02:58 - 【外汇早评】美通胀数据走低,美元调整

原标题:【外汇早评】美通胀数据走低,美元调整昨日美国方面公布了新一期的核心PCE物价指数数据,同比增长1.6%,低于前值和预期值的1.7%,距离美联储的通胀目标2%继续走低,通胀压力较低,且此前美国一季度GDP初值中的消费部分下滑明显,因此市场对美联储后续更可能降息的政策…...

2024/5/8 6:01:22 - 【原油贵金属周评】原油多头拥挤,价格调整

原标题:【原油贵金属周评】原油多头拥挤,价格调整本周国际劳动节,我们喜迎四天假期,但是整个金融市场确实流动性充沛,大事频发,各个商品波动剧烈。美国方面,在本周四凌晨公布5月份的利率决议和新闻发布会,维持联邦基金利率在2.25%-2.50%不变,符合市场预期。同时美联储…...

2024/5/7 9:45:25 - 【外汇周评】靓丽非农不及疲软通胀影响

原标题:【外汇周评】靓丽非农不及疲软通胀影响在刚结束的周五,美国方面公布了新一期的非农就业数据,大幅好于前值和预期,新增就业重新回到20万以上。具体数据: 美国4月非农就业人口变动 26.3万人,预期 19万人,前值 19.6万人。 美国4月失业率 3.6%,预期 3.8%,前值 3…...

2024/5/4 23:54:56 - 【原油贵金属早评】库存继续增加,油价收跌

原标题:【原油贵金属早评】库存继续增加,油价收跌周三清晨公布美国当周API原油库存数据,上周原油库存增加281万桶至4.692亿桶,增幅超过预期的74.4万桶。且有消息人士称,沙特阿美据悉将于6月向亚洲炼油厂额外出售更多原油,印度炼油商预计将每日获得至多20万桶的额外原油供…...

2024/5/7 14:25:14 - 【外汇早评】日本央行会议纪要不改日元强势

原标题:【外汇早评】日本央行会议纪要不改日元强势近两日日元大幅走强与近期市场风险情绪上升,避险资金回流日元有关,也与前一段时间的美日贸易谈判给日本缓冲期,日本方面对汇率问题也避免继续贬值有关。虽然今日早间日本央行公布的利率会议纪要仍然是支持宽松政策,但这符…...

2024/5/4 23:54:56 - 【原油贵金属早评】欧佩克稳定市场,填补伊朗问题的影响

原标题:【原油贵金属早评】欧佩克稳定市场,填补伊朗问题的影响近日伊朗局势升温,导致市场担忧影响原油供给,油价试图反弹。此时OPEC表态稳定市场。据消息人士透露,沙特6月石油出口料将低于700万桶/日,沙特已经收到石油消费国提出的6月份扩大出口的“适度要求”,沙特将满…...

2024/5/4 23:55:05 - 【外汇早评】美欲与伊朗重谈协议

原标题:【外汇早评】美欲与伊朗重谈协议美国对伊朗的制裁遭到伊朗的抗议,昨日伊朗方面提出将部分退出伊核协议。而此行为又遭到欧洲方面对伊朗的谴责和警告,伊朗外长昨日回应称,欧洲国家履行它们的义务,伊核协议就能保证存续。据传闻伊朗的导弹已经对准了以色列和美国的航…...

2024/5/4 23:54:56 - 【原油贵金属早评】波动率飙升,市场情绪动荡

原标题:【原油贵金属早评】波动率飙升,市场情绪动荡因中美贸易谈判不安情绪影响,金融市场各资产品种出现明显的波动。随着美国与中方开启第十一轮谈判之际,美国按照既定计划向中国2000亿商品征收25%的关税,市场情绪有所平复,已经开始接受这一事实。虽然波动率-恐慌指数VI…...

2024/5/7 11:36:39 - 【原油贵金属周评】伊朗局势升温,黄金多头跃跃欲试

原标题:【原油贵金属周评】伊朗局势升温,黄金多头跃跃欲试美国和伊朗的局势继续升温,市场风险情绪上升,避险黄金有向上突破阻力的迹象。原油方面稍显平稳,近期美国和OPEC加大供给及市场需求回落的影响,伊朗局势并未推升油价走强。近期中美贸易谈判摩擦再度升级,美国对中…...

2024/5/4 23:54:56 - 【原油贵金属早评】市场情绪继续恶化,黄金上破

原标题:【原油贵金属早评】市场情绪继续恶化,黄金上破周初中国针对于美国加征关税的进行的反制措施引发市场情绪的大幅波动,人民币汇率出现大幅的贬值动能,金融市场受到非常明显的冲击。尤其是波动率起来之后,对于股市的表现尤其不安。隔夜美国股市出现明显的下行走势,这…...

2024/5/6 1:40:42 - 【外汇早评】美伊僵持,风险情绪继续升温

原标题:【外汇早评】美伊僵持,风险情绪继续升温昨日沙特两艘油轮再次发生爆炸事件,导致波斯湾局势进一步恶化,市场担忧美伊可能会出现摩擦生火,避险品种获得支撑,黄金和日元大幅走强。美指受中美贸易问题影响而在低位震荡。继5月12日,四艘商船在阿联酋领海附近的阿曼湾、…...

2024/5/4 23:54:56 - 【原油贵金属早评】贸易冲突导致需求低迷,油价弱势

原标题:【原油贵金属早评】贸易冲突导致需求低迷,油价弱势近日虽然伊朗局势升温,中东地区几起油船被袭击事件影响,但油价并未走高,而是出于调整结构中。由于市场预期局势失控的可能性较低,而中美贸易问题导致的全球经济衰退风险更大,需求会持续低迷,因此油价调整压力较…...

2024/5/8 20:48:49 - 氧生福地 玩美北湖(上)——为时光守候两千年

原标题:氧生福地 玩美北湖(上)——为时光守候两千年一次说走就走的旅行,只有一张高铁票的距离~ 所以,湖南郴州,我来了~ 从广州南站出发,一个半小时就到达郴州西站了。在动车上,同时改票的南风兄和我居然被分到了一个车厢,所以一路非常愉快地聊了过来。 挺好,最起…...

2024/5/7 9:26:26 - 氧生福地 玩美北湖(中)——永春梯田里的美与鲜

原标题:氧生福地 玩美北湖(中)——永春梯田里的美与鲜一觉醒来,因为大家太爱“美”照,在柳毅山庄去寻找龙女而错过了早餐时间。近十点,向导坏坏还是带着饥肠辘辘的我们去吃郴州最富有盛名的“鱼头粉”。说这是“十二分推荐”,到郴州必吃的美食之一。 哇塞!那个味美香甜…...

2024/5/4 23:54:56 - 氧生福地 玩美北湖(下)——奔跑吧骚年!

原标题:氧生福地 玩美北湖(下)——奔跑吧骚年!让我们红尘做伴 活得潇潇洒洒 策马奔腾共享人世繁华 对酒当歌唱出心中喜悦 轰轰烈烈把握青春年华 让我们红尘做伴 活得潇潇洒洒 策马奔腾共享人世繁华 对酒当歌唱出心中喜悦 轰轰烈烈把握青春年华 啊……啊……啊 两…...

2024/5/8 19:33:07 - 扒开伪装医用面膜,翻六倍价格宰客,小姐姐注意了!

原标题:扒开伪装医用面膜,翻六倍价格宰客,小姐姐注意了!扒开伪装医用面膜,翻六倍价格宰客!当行业里的某一品项火爆了,就会有很多商家蹭热度,装逼忽悠,最近火爆朋友圈的医用面膜,被沾上了污点,到底怎么回事呢? “比普通面膜安全、效果好!痘痘、痘印、敏感肌都能用…...

2024/5/5 8:13:33 - 「发现」铁皮石斛仙草之神奇功效用于医用面膜

原标题:「发现」铁皮石斛仙草之神奇功效用于医用面膜丽彦妆铁皮石斛医用面膜|石斛多糖无菌修护补水贴19大优势: 1、铁皮石斛:自唐宋以来,一直被列为皇室贡品,铁皮石斛生于海拔1600米的悬崖峭壁之上,繁殖力差,产量极低,所以古代仅供皇室、贵族享用 2、铁皮石斛自古民间…...

2024/5/8 20:38:49 - 丽彦妆\医用面膜\冷敷贴轻奢医学护肤引导者

原标题:丽彦妆\医用面膜\冷敷贴轻奢医学护肤引导者【公司简介】 广州华彬企业隶属香港华彬集团有限公司,专注美业21年,其旗下品牌: 「圣茵美」私密荷尔蒙抗衰,产后修复 「圣仪轩」私密荷尔蒙抗衰,产后修复 「花茵莳」私密荷尔蒙抗衰,产后修复 「丽彦妆」专注医学护…...

2024/5/4 23:54:58 - 广州械字号面膜生产厂家OEM/ODM4项须知!

原标题:广州械字号面膜生产厂家OEM/ODM4项须知!广州械字号面膜生产厂家OEM/ODM流程及注意事项解读: 械字号医用面膜,其实在我国并没有严格的定义,通常我们说的医美面膜指的应该是一种「医用敷料」,也就是说,医用面膜其实算作「医疗器械」的一种,又称「医用冷敷贴」。 …...

2024/5/6 21:42:42 - 械字号医用眼膜缓解用眼过度到底有无作用?

原标题:械字号医用眼膜缓解用眼过度到底有无作用?医用眼膜/械字号眼膜/医用冷敷眼贴 凝胶层为亲水高分子材料,含70%以上的水分。体表皮肤温度传导到本产品的凝胶层,热量被凝胶内水分子吸收,通过水分的蒸发带走大量的热量,可迅速地降低体表皮肤局部温度,减轻局部皮肤的灼…...

2024/5/4 23:54:56 - 配置失败还原请勿关闭计算机,电脑开机屏幕上面显示,配置失败还原更改 请勿关闭计算机 开不了机 这个问题怎么办...

解析如下:1、长按电脑电源键直至关机,然后再按一次电源健重启电脑,按F8健进入安全模式2、安全模式下进入Windows系统桌面后,按住“winR”打开运行窗口,输入“services.msc”打开服务设置3、在服务界面,选中…...

2022/11/19 21:17:18 - 错误使用 reshape要执行 RESHAPE,请勿更改元素数目。

%读入6幅图像(每一幅图像的大小是564*564) f1 imread(WashingtonDC_Band1_564.tif); subplot(3,2,1),imshow(f1); f2 imread(WashingtonDC_Band2_564.tif); subplot(3,2,2),imshow(f2); f3 imread(WashingtonDC_Band3_564.tif); subplot(3,2,3),imsho…...

2022/11/19 21:17:16 - 配置 已完成 请勿关闭计算机,win7系统关机提示“配置Windows Update已完成30%请勿关闭计算机...

win7系统关机提示“配置Windows Update已完成30%请勿关闭计算机”问题的解决方法在win7系统关机时如果有升级系统的或者其他需要会直接进入一个 等待界面,在等待界面中我们需要等待操作结束才能关机,虽然这比较麻烦,但是对系统进行配置和升级…...

2022/11/19 21:17:15 - 台式电脑显示配置100%请勿关闭计算机,“准备配置windows 请勿关闭计算机”的解决方法...

有不少用户在重装Win7系统或更新系统后会遇到“准备配置windows,请勿关闭计算机”的提示,要过很久才能进入系统,有的用户甚至几个小时也无法进入,下面就教大家这个问题的解决方法。第一种方法:我们首先在左下角的“开始…...

2022/11/19 21:17:14 - win7 正在配置 请勿关闭计算机,怎么办Win7开机显示正在配置Windows Update请勿关机...

置信有很多用户都跟小编一样遇到过这样的问题,电脑时发现开机屏幕显现“正在配置Windows Update,请勿关机”(如下图所示),而且还需求等大约5分钟才干进入系统。这是怎样回事呢?一切都是正常操作的,为什么开时机呈现“正…...

2022/11/19 21:17:13 - 准备配置windows 请勿关闭计算机 蓝屏,Win7开机总是出现提示“配置Windows请勿关机”...

Win7系统开机启动时总是出现“配置Windows请勿关机”的提示,没过几秒后电脑自动重启,每次开机都这样无法进入系统,此时碰到这种现象的用户就可以使用以下5种方法解决问题。方法一:开机按下F8,在出现的Windows高级启动选…...

2022/11/19 21:17:12 - 准备windows请勿关闭计算机要多久,windows10系统提示正在准备windows请勿关闭计算机怎么办...

有不少windows10系统用户反映说碰到这样一个情况,就是电脑提示正在准备windows请勿关闭计算机,碰到这样的问题该怎么解决呢,现在小编就给大家分享一下windows10系统提示正在准备windows请勿关闭计算机的具体第一种方法:1、2、依次…...

2022/11/19 21:17:11 - 配置 已完成 请勿关闭计算机,win7系统关机提示“配置Windows Update已完成30%请勿关闭计算机”的解决方法...

今天和大家分享一下win7系统重装了Win7旗舰版系统后,每次关机的时候桌面上都会显示一个“配置Windows Update的界面,提示请勿关闭计算机”,每次停留好几分钟才能正常关机,导致什么情况引起的呢?出现配置Windows Update…...

2022/11/19 21:17:10 - 电脑桌面一直是清理请关闭计算机,windows7一直卡在清理 请勿关闭计算机-win7清理请勿关机,win7配置更新35%不动...

只能是等着,别无他法。说是卡着如果你看硬盘灯应该在读写。如果从 Win 10 无法正常回滚,只能是考虑备份数据后重装系统了。解决来方案一:管理员运行cmd:net stop WuAuServcd %windir%ren SoftwareDistribution SDoldnet start WuA…...

2022/11/19 21:17:09 - 计算机配置更新不起,电脑提示“配置Windows Update请勿关闭计算机”怎么办?

原标题:电脑提示“配置Windows Update请勿关闭计算机”怎么办?win7系统中在开机与关闭的时候总是显示“配置windows update请勿关闭计算机”相信有不少朋友都曾遇到过一次两次还能忍但经常遇到就叫人感到心烦了遇到这种问题怎么办呢?一般的方…...

2022/11/19 21:17:08 - 计算机正在配置无法关机,关机提示 windows7 正在配置windows 请勿关闭计算机 ,然后等了一晚上也没有关掉。现在电脑无法正常关机...

关机提示 windows7 正在配置windows 请勿关闭计算机 ,然后等了一晚上也没有关掉。现在电脑无法正常关机以下文字资料是由(历史新知网www.lishixinzhi.com)小编为大家搜集整理后发布的内容,让我们赶快一起来看一下吧!关机提示 windows7 正在配…...

2022/11/19 21:17:05 - 钉钉提示请勿通过开发者调试模式_钉钉请勿通过开发者调试模式是真的吗好不好用...

钉钉请勿通过开发者调试模式是真的吗好不好用 更新时间:2020-04-20 22:24:19 浏览次数:729次 区域: 南阳 > 卧龙 列举网提醒您:为保障您的权益,请不要提前支付任何费用! 虚拟位置外设器!!轨迹模拟&虚拟位置外设神器 专业用于:钉钉,外勤365,红圈通,企业微信和…...

2022/11/19 21:17:05 - 配置失败还原请勿关闭计算机怎么办,win7系统出现“配置windows update失败 还原更改 请勿关闭计算机”,长时间没反应,无法进入系统的解决方案...

前几天班里有位学生电脑(windows 7系统)出问题了,具体表现是开机时一直停留在“配置windows update失败 还原更改 请勿关闭计算机”这个界面,长时间没反应,无法进入系统。这个问题原来帮其他同学也解决过,网上搜了不少资料&#x…...

2022/11/19 21:17:04 - 一个电脑无法关闭计算机你应该怎么办,电脑显示“清理请勿关闭计算机”怎么办?...

本文为你提供了3个有效解决电脑显示“清理请勿关闭计算机”问题的方法,并在最后教给你1种保护系统安全的好方法,一起来看看!电脑出现“清理请勿关闭计算机”在Windows 7(SP1)和Windows Server 2008 R2 SP1中,添加了1个新功能在“磁…...

2022/11/19 21:17:03 - 请勿关闭计算机还原更改要多久,电脑显示:配置windows更新失败,正在还原更改,请勿关闭计算机怎么办...

许多用户在长期不使用电脑的时候,开启电脑发现电脑显示:配置windows更新失败,正在还原更改,请勿关闭计算机。。.这要怎么办呢?下面小编就带着大家一起看看吧!如果能够正常进入系统,建议您暂时移…...

2022/11/19 21:17:02 - 还原更改请勿关闭计算机 要多久,配置windows update失败 还原更改 请勿关闭计算机,电脑开机后一直显示以...

配置windows update失败 还原更改 请勿关闭计算机,电脑开机后一直显示以以下文字资料是由(历史新知网www.lishixinzhi.com)小编为大家搜集整理后发布的内容,让我们赶快一起来看一下吧!配置windows update失败 还原更改 请勿关闭计算机&#x…...

2022/11/19 21:17:01 - 电脑配置中请勿关闭计算机怎么办,准备配置windows请勿关闭计算机一直显示怎么办【图解】...

不知道大家有没有遇到过这样的一个问题,就是我们的win7系统在关机的时候,总是喜欢显示“准备配置windows,请勿关机”这样的一个页面,没有什么大碍,但是如果一直等着的话就要两个小时甚至更久都关不了机,非常…...

2022/11/19 21:17:00 - 正在准备配置请勿关闭计算机,正在准备配置windows请勿关闭计算机时间长了解决教程...

当电脑出现正在准备配置windows请勿关闭计算机时,一般是您正对windows进行升级,但是这个要是长时间没有反应,我们不能再傻等下去了。可能是电脑出了别的问题了,来看看教程的说法。正在准备配置windows请勿关闭计算机时间长了方法一…...

2022/11/19 21:16:59 - 配置失败还原请勿关闭计算机,配置Windows Update失败,还原更改请勿关闭计算机...

我们使用电脑的过程中有时会遇到这种情况,当我们打开电脑之后,发现一直停留在一个界面:“配置Windows Update失败,还原更改请勿关闭计算机”,等了许久还是无法进入系统。如果我们遇到此类问题应该如何解决呢࿰…...

2022/11/19 21:16:58 - 如何在iPhone上关闭“请勿打扰”

Apple’s “Do Not Disturb While Driving” is a potentially lifesaving iPhone feature, but it doesn’t always turn on automatically at the appropriate time. For example, you might be a passenger in a moving car, but your iPhone may think you’re the one dri…...

2022/11/19 21:16:57